Inc. PLB PCI Full Bridge Product Specification

PLB PCI Full Bridge (v1.00a)

DS508 March 21, 2006 www.xilinx.com 13

Product Specification

E

AR

L

Y

ACCESS

G61

Include configuration

functionality via IPIF

transactions

C_INCLUDE_

PCI_CONFIG

0 = Not included

1 = Included

1 integer

G62

Number of IDSEL

signals supported

C_NUM_

IDSEL

1 to 16 8 integer

G63

PCI address bit that PCI

v3.0 core IDSEL is

connected to

C_BRIDGE_

IDSEL_ADDR_

BIT

31 down to 16

Must be <= 15 +

C_NUM_IDSEL.

AD(31 down to 0) index

labeling

16 integer

IPIF Parameters Group

G64

PLB master ID bus

width (set automatically

by XPS)

C_PLB_MID_

WIDTH

log

2

(C_PLB_NUM_MA

STERS)

3 integer

G65

Number of masters on

PLB bus (set

automatically by XPS)

C_PLB_NUM_

MASTERS

1-16 8 integer

G66 PLB Address width

C_PLB_

AWIDTH

32 (only allowed value 32 integer

G67 PLB Data width

C_PLB_

DWIDTH

64 (only allowed value 64 integer

G68

Specifies the target

technology

C_FAMILY

See PLB IPIF data

sheet

virtex2 string

Notes:

1. The range specified must comprise a complete, contiguous power of two range, such that the range = 2

n

and

the n least significant bits of the Base Address are zero.

2. The minimum address range specified by C_BASEADDR and C_HIGHADDR must be at least 0x1FF.

C_BASEADDR must be a multiple of the range, where the range is C_HIGHADDR - C_BASEADDR + 1.

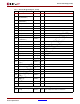

Table 1: PLB PCI Bridge Interface Design Parameters (Contd)

Generic

Feature /

Description

Parameter

Name

Allowable Values

Default

Value

VHDL

Type