Datasheet

Table Of Contents

T

T

T

S

S

S

6

6

6

4

4

4

M

M

M

L

L

L

Q

Q

Q

6

6

6

4

4

4

V

V

V

8

8

8

J

J

J

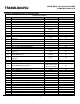

240PIN DDR2 800 Unbuffered DIMM

512MB With 64Mx8 CL5

Transcend Information Inc.

11

37

Internal write to read command delay(=tWTR)

7.5ns 1E

38

Internal read to precharge command delay(=tRTP)

7.5ns 1E

39

Memory analysis probe characteristics

- 00

40

Extension of Byte41 tRC and Byte42 tRFC

tRC(51.5ns) 30

41

DDR SDRAM Minimum Active to Active/Auto Refresh

Time(tRC)

51ns 33

42

DDR SDRAM Minimum Auto-Refresh to

Active/Auto-Refresh Command Period (tRFC)

105ns 69

43

DDR SDRAM Maximum Device Cycle Time (tCK max)

8ns 80

44

DDR SDRAM DQS-DQ Skew for DQS and associated

DQ signals (tDQSQ max)

0.20ns 14

45

DDR SDRAM Read Data Hold Skew Factor (tQHS)

0.3ns 1E

46

PLL Relock Time

- 00

47~61

Superset Information

- 00

62 SPD Data Revision Code REV 1.2 12

63 Checksum for Bytes 0-62 - 52

64-71 Manufacturers JEDEC ID Transcend 01, 4F

72 Manufacturing Location T 54

54 53 36 34 4D 4C

51 36 34 56 38 4A

73-90 Manufacturers Part Number TS64MLQ64V8J

20 20 20 20 20 20

91-92 Revision Code - -

93-94 Manufacturing Date By Manufacturer Variable

95-98 Assembly Serial Number By Manufacturer Variable

99-127 Manufacturer Specific Data - -

128~255

Open for customer use

Undefined -