Users Manual Part 2

Table Of Contents

- 1 Physical Description

- 2 Interfaces Description

- 2.1 Interfaces Parameter Definitions

- 2.2 Interfaces Detail Description

- 2.2.1 Power Supply Interface

- 2.2.2 Touchscreen Interface

- 2.2.3 Display Interface

- 2.2.4 Camera Interfaces

- 2.2.5 Audio Interface

- 2.2.6 USB & DisplayPort Interface

- 2.2.7 PCIe Interface

- 2.2.8 SSC Interface

- 2.2.9 SDIO Interface

- 2.2.10 QUP Interface

- 2.2.11 Power on Interface

- 2.2.12 Reset Interface

- 2.2.13 Keys Interface

- 2.2.14 Sensor Interrupt Interface

- 2.2.15 Debug UART Interface

- 2.2.16 Battery Interface

- 2.2.17 ADCs Interface

- 2.2.18 PWMs and LED Current Driver Interface

- 2.2.19 Antenna Interface

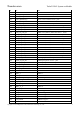

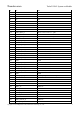

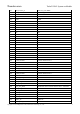

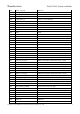

- 3 Connector PIN Summary

- 4 Electrical Characteristics

Thundercomm TurboX C865 System on Module

Copyright © 2018 All Rights Reserved, Thundercomm Technology Co., Ltd.

3

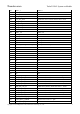

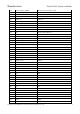

E9

NC

NC

E10

NC

NC

E11

PCIE1_RX0_P

PCIe 1 Gen 3 receive 0 – plus

E12

PCIE1_RX1_M

PCIe 1 Gen 3 receive 1 – minus

E13

PCIE1_REFCLK_P

PCIe 1 Gen 3 reference clock – plus

E14

PCIE1_TX1_M

PCIe 1 Gen 3 transmit 1 – minus

E15

PCIE1_TX0_P

PCIe 1 Gen 3 transmit 0 – plus

E16 CSI2_B2_LN3_P MIPI CSI 2 (DPHY), differential lane 3 – plus

E17 CSI2_A2_LN2_M MIPI CSI 2 (DPHY), differential lane 2 – minus

E18

CSI2_A1_LN1_P

MIPI CSI 2 (DPHY), differential lane 1 – plus

E19

CSI2_C0_LN0_M

MIPI CSI 2 (DPHY), differential lane 0 – minus

E20

CSI2_NC_CLK_P

MIPI CSI 2 (DPHY), differential clock – plus

E21

CSI4_C2_LN3_M

MIPI CSI 4 (DPHY), differential lane 3 – minus

E22

CSI4_C1_LN2_P

MIPI CSI 4 (DPHY), differential lane 2 – plus

E23

CSI4_C0_LN0_M

MIPI CSI 4 (DPHY), differential lane 0 – minus

E24

CSI4_NC_CLK_P

MIPI CSI 4 (DPHY), differential clock – plus

E25

CSI4_B1_LN1_M

MIPI CSI 4 (DPHY), differential lane 1 – minus

E26

CSI5_B2_LN3_P

MIPI CSI 5 (DPHY), differential lane 3 – plus

E27 CSI5_C0_LN0_M MIPI CSI 5 (DPHY), differential lane 0 – minus

E28 CSI5_C1_LN2_P MIPI CSI 5 (DPHY), differential lane 2 – plus

E29

CSI5_B1_LN1_M

MIPI CSI 5 (DPHY), differential lane 1 – minus

E30

CSI5_NC_CLK_P

MIPI CSI 5 (DPHY), differential clock – plus

E31

USB1_HS_DP

USB high-speed 1 data – plus

E32

USB1_SS_TX_M

USB super-speed 1 receive – plus

E33

USB1_SS_RX_P

USB super-speed 1 receive – plus

E34

PMIC_SPMI_CLK

SPMI clock

E35

PMIC_SPMI_DATA

SPMI data

E36 GPIO_10_C GPIO 10

E37

note1

GPIO 145 See below table

E38 GPIO_3 GPIO 3

E39

GPIO_1

GPIO 1

E40

SDM_FAST_BOOT_1

Boot configuration 1

E41

MIPI_ERR_FG

GPIO 46

E42

TS_I2C_SDA

Data of I2C

E43

APPS_I2C_SCL

I2C SCL for sensor

E44

GPIO_71_C

GPIO 71

E45

GPIO_72_C

GPIO 72

E46 USB_CC2 CC2 of Type C

E47 USB_VBUS VBUS of Type C

E48

USB_VBUS

VBUS of Type C

E49

USB_VBUS

VBUS of Type C

E50

USB_VBUS

VBUS of Type C

F1

NC

NC