Users Manual Part 2

Table Of Contents

- 1 Physical Description

- 2 Interfaces Description

- 2.1 Interfaces Parameter Definitions

- 2.2 Interfaces Detail Description

- 2.2.1 Power Supply Interface

- 2.2.2 Touchscreen Interface

- 2.2.3 Display Interface

- 2.2.4 Camera Interfaces

- 2.2.5 Audio Interface

- 2.2.6 USB & DisplayPort Interface

- 2.2.7 PCIe Interface

- 2.2.8 SSC Interface

- 2.2.9 SDIO Interface

- 2.2.10 QUP Interface

- 2.2.11 Power on Interface

- 2.2.12 Reset Interface

- 2.2.13 Keys Interface

- 2.2.14 Sensor Interrupt Interface

- 2.2.15 Debug UART Interface

- 2.2.16 Battery Interface

- 2.2.17 ADCs Interface

- 2.2.18 PWMs and LED Current Driver Interface

- 2.2.19 Antenna Interface

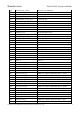

- 3 Connector PIN Summary

- 4 Electrical Characteristics

Thundercomm TurboX C865 System on Module

Copyright © 2018 All Rights Reserved, Thundercomm Technology Co., Ltd.

2

A37

PMK8002_RF_CLK2

RF clock 2 for PMK8002

A38

DISP0_RESET_N

LCM reset

A39

SDM_FAST_BOOT_2

Boot configuration 2

A40

DEBUG_PMIC_PKD_N

Power key

A41

DEBUG_KEY_VOL_UP_N

Volume up key

A42

DEBUG_KEY_VOL_DOWN_N

Volume down key

A43

PM855_USB_SBU1

SBU1 of Type C

A44 PM855_USB_SBU2 SBU2 of Type C

A45 CBL_PWR_N CBL_PWR

A46

GPIO_8_C

GPIO 8

A47

VDISP_P_OUT

LCM Backlight Positive

A48

VDISP_M_OUT

LCM Backlight Minus

A49

VREG_L11C_3P3

VREG_L11C_3P3

A50

VREG_L9C_2P96

VREG_L9C_2P96

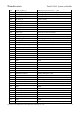

B1

GPIO_168

GPIO 168

B2

GND

GND

B3

GND

GND

B4

VREG_L5C_1P8

VREG_L5C_1P8

B5 VREG_L5C_1P8 VREG_L5C_1P8

B6 GPIO_135 GPIO 135

B7

GPIO_162

GPIO 162

B8

GPIO_163

GPIO 163

B9

GPIO_12

GPIO 12

B10

GPIO_13

GPIO 13

B11

SDC2_DATA_3

Secure digital controller 2 data bit 3

B12

SDC2_DATA_0

Secure digital controller 2 data bit 0

B13

SDC2_CLK_CONN

Secure digital controller 2 clock

B14 CSI1_C2_LN3_M MIPI CSI 1 (DPHY), differential lane 3 – minus

B15 CSI1_C1_LN2_P MIPI CSI 1 (DPHY), differential lane 2 – plus

B16 CSI1_C0_LN0_M MIPI CSI 1 (DPHY), differential lane 0 – minus

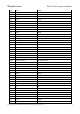

B17

CSI1_NC_CLK_P

MIPI CSI 1 (DPHY), differential clock – plus

B18

CSI1_B1_LN1_M

MIPI CSI 1 (DPHY), differential lane 1 – minus

B19

CSI3_B0_LN0_P

MIPI CSI 3 (DPHY), differential lane 0 – plus

B20

CSI3_A0_CLK_M

MIPI CSI 3 (DPHY), differential clock – minus

B21

CSI3_B2_LN3_P

MIPI CSI 3 (DPHY), differential lane 3 – plus

B22

CSI3_A2_LN2_M

MIPI CSI 3 (DPHY), differential lane 2 – minus

B23

CSI3_A1_LN1_P

MIPI CSI 3 (DPHY), differential lane 1 – plus

B24 DSI1_A2_LN2_P MIPI DSI 1 (DPHY), differential lane 2 – plus

B25 DSI1_C1_CLK_M MIPI DSI 1 (DPHY), differential clock – minus

B26

DSI1_A0_LN0_P

MIPI DSI 1 (DPHY), differential lane 0 – plus

B27

DSI1_A1_LN1_M

MIPI DSI 1 (DPHY), differential lane 1 – minus

B28

DSI1_C2_LN3_P

MIPI DSI 1 (DPHY), differential lane 3 – plus

B29

USB0_HS_DP

USB high-speed 0 data – plus