Marine Radio - Marine Radio Decoder User Manual

INTER0

INTER1

INTER3

INTER2

Base 0

Base 2

Base 4

Base 6

INTER2

INTER3

INTER1

INTER0

EDMA3

63 0

INTER3

INTER2

INTER1

INTER0

Kernel

63 0

TCP

Memory

Endian_Intr=1

Endianness

manager

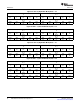

7.1.3.2 ENDIAN_INTR = 0

INTER1

INTER0

INTER2

INTER3

Base 0

Base 2

Base 4

Base 6

INTER3

INTER2

INTER0

INTER1

EDMA3

63 0

INTER3

INTER2

INTER1

INTER0

Kernel

63 0

TCP

Memory

Endian_Intr=0

Endianness

manager

Endianness

www.ti.com

Figure 83. Interleaver Indexes in DSP Memory (ENDIAN_INTR = 1)

They have to be swapped as described in Figure 84 and Figure 85 .

Figure 84. Data Source - EDMA3 (ENDIAN_INTR = 1)

63 48 47 32 31 16 15 1

INTER0 INTER1 INTER2 INTER3

Figure 85. Data Destination - Kernel (ENDIAN_INTR = 1)

63 48 47 32 31 16 15 1

INTER3 INTER2 INTER1 INTER0

If ENDIAN_INTR = 0, data are saved in word packed format (32 bits) in the DSP (see Table 36 ).

Table 36. Interleaver Indexes in DSP Memory

(ENDIAN_INTR = 0)

Address (hex bytes) Data

Base INTER1

Base + 2 INTER0

Base + 4 INTER3

Base + 6 INTER2

Figure 86. Interleaver Indexes in DSP Memory (ENDIAN_INTR = 0)

They have to be swapped as described in Figure 87 and Figure 88 .

56 TMS320C6457 Turbo-Decoder Coprocessor 2 SPRUGK1 – March 2009

Submit Documentation Feedback