Datasheet

Table Of Contents

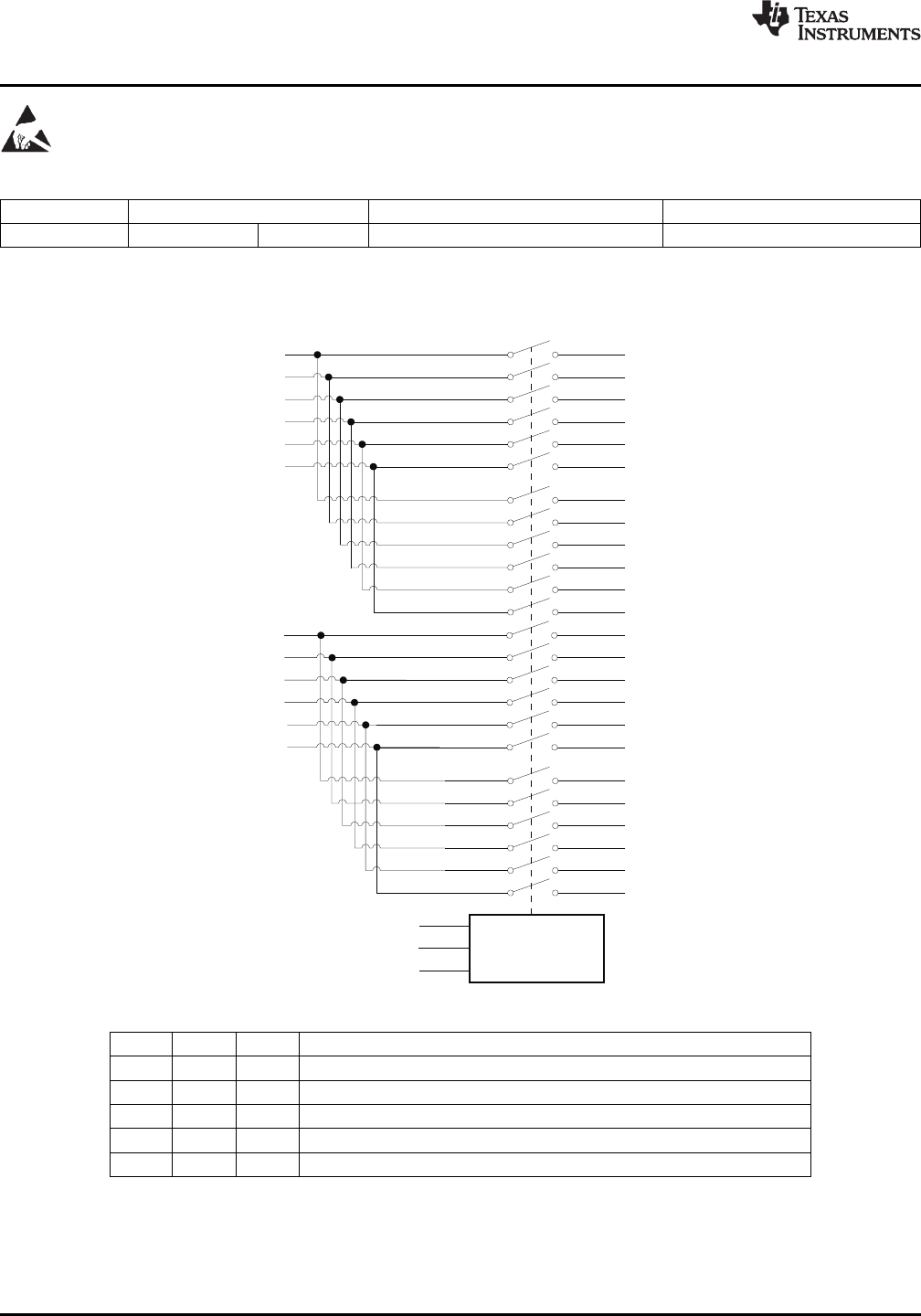

B

0

B

1

B

2

B

3

B

4

B

5

C

0

C

1

C

2

C

3

C

4

C

5

C

6

C

7

C

8

C

9

C

10

C

11

A

0

A

1

A

2

A

3

A

4

A

5

SEL1

Control Logic

SEL2

B

6

B

7

B

8

B

9

B

10

B

11

A

6

A

7

A

8

A

9

A

10

A

11

EN

TS3DDR3812

SCDS314A –FEBRUARY 2011– REVISED MARCH 2011

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

ORDERING INFORMATION

T

A

PACKAGE

(1)

ORDERABLE PART NUMBER TOP-SIDE MARKING

–40°C to 85°C QFN - RUA Tape and Reel TS3DDR3812RUAR SL812

(1) Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at

www.ti.com/sc/package.

LOGIC DIAGRAM

FUNCTION TABLE

EN SEL1 SEL2 FUNCTION

L X X A

0

to A

11

, B

0

to B

11

, and C

0

to C

11

are Hi-Z

H L L A

0

to A

5

= B

0

to B

5

and A

6

to A

11

= B

6

to B

11

H L H A

0

to A

5

= B

0

to B

5

and A

6

to A

11

= C

6

to C

11

H H L A

0

to A

5

= C

0

to C

5

and A

6

to A

11

= B

6

to B

11

H H H A

0

to A

5

= C

0

to C

5

and A

6

to A

11

= C

6

to C

11

2 Submit Documentation Feedback Copyright © 2011, Texas Instruments Incorporated

Product Folder Link(s) :TS3DDR3812