Serial RapidIO (SRIO) User's Guide

www.ti.com

SRIO Registers

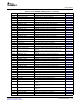

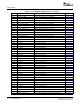

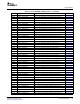

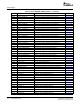

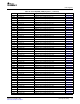

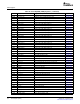

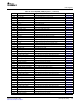

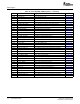

Table 40. Serial RapidIO (SRIO) Registers (continued)

Offset Acronym Register Description Section

030Ch INTDST3_DECODE INTDST Interrupt Status Decode Register 3 Section 5.31

0310h INTDST4_DECODE INTDST Interrupt Status Decode Register 4 Section 5.31

0314h INTDST5_DECODE INTDST Interrupt Status Decode Register 5 Section 5.31

0318h INTDST6_DECODE INTDST Interrupt Status Decode Register 6 Section 5.31

031Ch INTDST7_DECODE INTDST Interrupt Status Decode Register 7 Section 5.31

0320h INTDST0_RATE_CNTL INTDST Interrupt Rate Control Register 0 Section 5.32

0324h INTDST1_RATE_CNTL INTDST Interrupt Rate Control Register 1 Section 5.32

0328h INTDST2_RATE_CNTL INTDST Interrupt Rate Control Register 2 Section 5.32

032Ch INTDST3_RATE_CNTL INTDST Interrupt Rate Control Register 3 Section 5.32

0330h INTDST4_RATE_CNTL INTDST Interrupt Rate Control Register 4 Section 5.32

0334h INTDST5_RATE_CNTL INTDST Interrupt Rate Control Register 5 Section 5.32

0338h INTDST6_RATE_CNTL INTDST Interrupt Rate Control Register 6 Section 5.32

033Ch INTDST7_RATE_CNTL INTDST Interrupt Rate Control Register 7 Section 5.32

0400h LSU1_REG0 LSU1 Control Register 0 Section 5.33

0404h LSU1_REG1 LSU1 Control Register 1 Section 5.34

0408h LSU1_REG2 LSU1 Control Register 2 Section 5.35

040Ch LSU1_REG3 LSU1 Control Register 3 Section 5.36

0410h LSU1_REG4 LSU1 Control Register 4 Section 5.37

0414h LSU1_REG5 LSU1 Control Register 5 Section 5.38

0418h LSU1_REG6 LSU1 Control Register 6 Section 5.39

041Ch LSU1_FLOW_MASKS LSU1 Congestion Control Flow Mask Register Section 5.40

0420h LSU2_REG0 LSU2 Control Register 0 Section 5.33

0424h LSU2_REG1 LSU2 Control Register 1 Section 5.34

0428h LSU2_REG2 LSU2 Control Register 2 Section 5.35

042Ch LSU2_REG3 LSU2 Control Register 3 Section 5.36

0430h LSU2_REG4 LSU2 Control Register 4 Section 5.37

0434h LSU2_REG5 LSU2 Control Register 5 Section 5.38

0438h LSU2_REG6 LSU2 Control Register 6 Section 5.39

043Ch LSU2_FLOW_MASKS1 LSU2 Congestion Control Flow Mask Register Section 5.40

0440h LSU3_REG0 LSU3 Control Register 0 Section 5.33

0444h LSU3_REG1 LSU3 Control Register 1 Section 5.34

0448h LSU3_REG2 LSU3 Control Register 2 Section 5.35

044Ch LSU3_REG3 LSU3 Control Register 3 Section 5.36

0450h LSU3_REG4 LSU3 Control Register 4 Section 5.37

0454h LSU3_REG5 LSU3 Control Register 5 Section 5.38

0458h LSU3_REG6 LSU3 Control Register 6 Section 5.39

045Ch LSU3_FLOW_MASKS2 LSU3 Congestion Control Flow Mask Register Section 5.40

0460h LSU4_REG0 LSU4 Control Register 0 Section 5.33

0464h LSU4_REG1 LSU4 Control Register 1 Section 5.34

0468h LSU4_REG2 LSU4 Control Register 2 Section 5.35

046Ch LSU4_REG3 LSU4 Control Register 3 Section 5.36

0470h LSU4_REG4 LSU4 Control Register 4 Section 5.37

0474h LSU4_REG5 LSU4 Control Register 5 Section 5.38 ≈

0478h LSU4_REG6 LSU4 Control Register 6 Section 5.39

047Ch LSU4_FLOW_MASKS3 LSU4 Congestion Control Flow Mask Register Section 5.40

0500h QUEUE0_TXDMA_HDP Queue Transmit DMA Head Descriptor Pointer Register 0 Section 5.41

104 Serial RapidIO (SRIO) SPRUE13A – September 2006

Submit Documentation Feedback