Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- DESCRIPTION

- TYPICAL APPLICATION

- ABSOLUTE MAXIMUM RATINGS

- THERMAL INFORMATION

- ELECTRICAL CHARACTERISTICS

- PIN CONFIGURATION

- TYPICAL CHARACTERISTICS

- APPLICATION INFORMATION

- GENERAL DESCRIPTION

- COMMUNICATION PROTOCOL

- COMMAND REGISTER

- GLOBAL INITIALIZATION AND ADDRESS ASSIGNMENT SEQUENCE

- GLOBAL READ AND WRITE

- GLOBAL CLEAR INTERRUPT

- GLOBAL SOFTWARE RESET

- INDIVIDUAL READ AND WRITE

- TEMPERATURE REGISTER

- CONFIGURATION REGISTER

- TEMPERATURE LIMIT REGISTERS

- TIMEOUT FUNCTION

- NOISE

- SMAART WIRE INTERFACE TIMING SPECIFICATIONS

- Revision History

Host

Device

(1)

Device

(2)

Device

(N)

RX

TX

Interface Logic Interface Logic Interface Logic

RX RX RX

TX TX TX

TMP104

SBOS564A –NOVEMBER 2011– REVISED NOVEMBER 2011

www.ti.com

Interrupt Functionality (INT_EN)

The TMP104 interrupts the host by disconnecting the bus and issuing an interrupt request by holding the bus low

if all of these conditions are met, as shown in Figure 13:

• INT_EN in the Configuration Register is set to '1';

• The temperature result is higher than the value in the T

HIGH

register or lower than the value in the T

LOW

register (as indicated by a '1' in either FL or FH);

• The bus is logic high and idle for more than 28 ms.

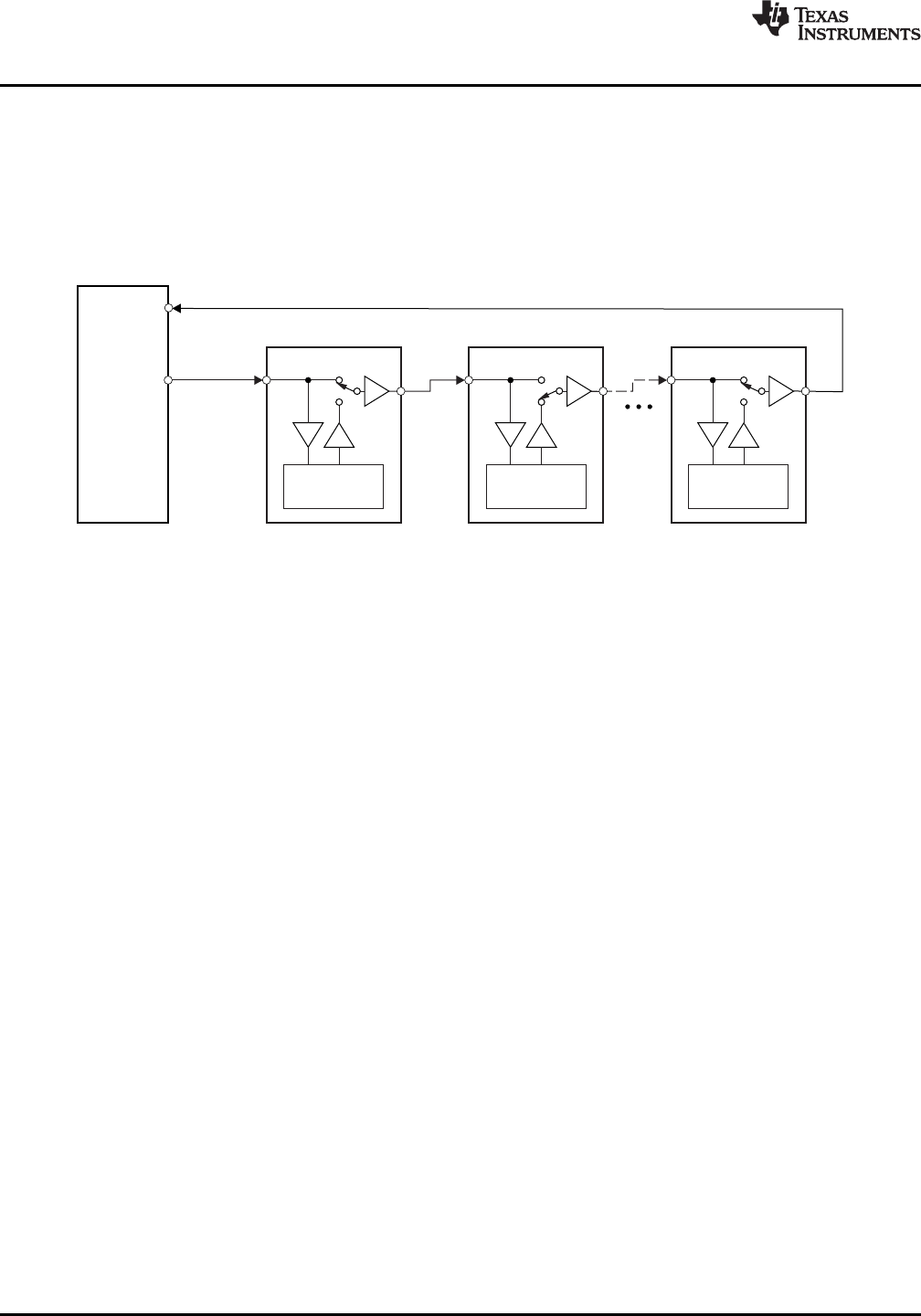

Figure 13. TMP104 Daisy-Chain:

Bus Status During an Interrupt Request (Logic Low) from Second Device

The interrupt on the bus is latched regardless of the status of LC. Writing a '1' to INT_EN automatically sets the

LC bit. The TMP104 holds the bus low until one of the following events happen:

• Global Interrupt Clear command received;

• Global Software Reset command received;

• A power-on reset event occurs.

Each of these events clears INT_EN; the TMP104 does not issue future interrupts until the host writes '1' to bit

D7 in the Configuration Register to re-enable future interrupts.

In a system with enabled interrupts, it is possible for a TMP104 on the bus to issue an interrupt at the same time

that the host starts a communication sequence. To avoid this scenario, it is recommended that the host should

check the status on the receiving side of the bus after transmitting the calibration byte. If it is '1', then the host

can continue with the communication. If it is '0', one of the TMP104 devices on the bus is issuing an alert and the

host must transmit a Global Interrupt Clear command.

14 Submit Documentation Feedback Copyright © 2011, Texas Instruments Incorporated

Product Folder Link(s): TMP104