Car Stereo System - Car Radio Digital Signal Processor User Manual

www.ti.com

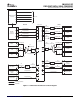

Megamodule

M

CFG SCR

S

M

M

S

TCP2

VCP2

S

McBSPs

S

UTOPIA

S

Timers

S

HPI

S

PCI

S

S

Bridge

7

GPIO

S

EMAC/MDIO

M

Data SCR

S

S

I2C

SS

PLL

Controllers

(A)

S

S

Device

Configuration

Registers

(A)

EDMA3 TC0

S

EDMA3 TC1

S

Serial RapidIO

S

S EDMA3 TC2

S

EDMA3 CC

SS

EDMA3 TC3

S

M

M

32

(SYSCLK3)

32 (SYSCLK2)

32 (SYSCLK2)

MUX

32

(SYSCLK2)

32

(SYSCLK2)

32 (SYSCLK2)

32 (SYSCLK2)

32

(SYSCLK3)

32

(SYSCLK2)

32 (SYSCLK2)

32-bit

(SYSCLK2)

Configuration Bus

Data Bus

MUX

MUX

32

(SYSCLK2)

32

(SYSCLK2)

32

(SYSCLK2)

32

(SYSCLK2)

A. Only accessible by the C64x+ Megamodule.

B. All clocks in this figure are generated by the PLL1 controller.

32

(SYSCLK3)

32

(SYSCLK3)

32

(SYSCLK3)

32

(SYSCLK3)

32

(SYSCLK3)

32

(SYSCLK3)

32

(SYSCLK3)

32

(SYSCLK3)

32

(SYSCLK3)

32

(SYSCLK2)

SM320C6455-EP

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS462B – SEPTEMBER 2007 – REVISED JANUARY 2008

Figure 4-2. C64x+ Megamodule - SCR Connection

Submit Documentation Feedback System Interconnect 85