Car Stereo System - Car Radio Digital Signal Processor User Manual

www.ti.com

SM320C6455-EP

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS462B – SEPTEMBER 2007 – REVISED JANUARY 2008

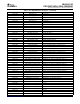

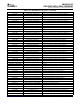

Table 7-112. RapidIO Control Registers (continued)

HEX ADDRESS RANGE ACRONYM REGISTER NAME

02D0 0610 RIO_QUEUE4_RXDMA_HDP Queue Receive DMA Head Descriptor Pointer Register 4

02D0 0614 RIO_QUEUE5_RXDMA_HDP Queue Receive DMA Head Descriptor Pointer Register 5

02D0 0618 RIO_QUEUE6_RXDMA_HDP Queue Receive DMA Head Descriptor Pointer Register 6

02D0 061C RIO_QUEUE7_RXDMA_HDP Queue Receive DMA Head Descriptor Pointer Register 7

02D0 0620 RIO_QUEUE8_RXDMA_HDP Queue Receive DMA Head Descriptor Pointer Register 8

02D0 0624 RIO_QUEUE9_RXDMA_HDP Queue Receive DMA Head Descriptor Pointer Register 9

02D0 0628 RIO_QUEUE10_RXDMA_HDP Queue Receive DMA Head Descriptor Pointer Register 10

02D0 062C RIO_QUEUE11_RXDMA_HDP Queue Receive DMA Head Descriptor Pointer Register 11

02D0 0630 RIO_QUEUE12_RXDMA_HDP Queue Receive DMA Head Descriptor Pointer Register 12

02D0 0634 RIO_QUEUE13_RXDMA_HDP Queue Receive DMA Head Descriptor Pointer Register 13

02D0 0638 RIO_QUEUE14_RXDMA_HDP Queue Receive DMA Head Descriptor Pointer Register 14

02D0 063C RIO_QUEUE15_RXDMA_HDP Queue Receive DMA Head Descriptor Pointer Register 15

02D0 0640 - 02D0 067C - Reserved

02D0 0680 RIO_QUEUE0_RXDMA_CP Queue Receive DMA Completion Pointer Register 0

02D0 0684 RIO_QUEUE1_RXDMA_CP Queue Receive DMA Completion Pointer Register 1

02D0 0688 RIO_QUEUE2_RXDMA_CP Queue Receive DMA Completion Pointer Register 2

02D0 068C RIO_QUEUE3_RXDMA_CP Queue Receive DMA Completion Pointer Register 3

02D0 0690 RIO_QUEUE4_RXDMA_CP Queue Receive DMA Completion Pointer Register 4

02D0 0694 RIO_QUEUE5_RXDMA_CP Queue Receive DMA Completion Pointer Register 5

02D0 0698 RIO_QUEUE6_RXDMA_CP Queue Receive DMA Completion Pointer Register 6

02D0 069C RIO_QUEUE7_RXDMA_CP Queue Receive DMA Completion Pointer Register 7

02D0 06A0 RIO_QUEUE8_RXDMA_CP Queue Receive DMA Completion Pointer Register 8

02D0 06A4 RIO_QUEUE9_RXDMA_CP Queue Receive DMA Completion Pointer Register 9

02D0 06A8 RIO_QUEUE10_RXDMA_CP Queue Receive DMA Completion Pointer Register 10

02D0 06AC RIO_QUEUE11_RXDMA_CP Queue Receive DMA Completion Pointer Register 11

02D0 06B0 RIO_QUEUE12_RXDMA_CP Queue Receive DMA Completion Pointer Register 12

02D0 06B4 RIO_QUEUE13_RXDMA_CP Queue Receive DMA Completion Pointer Register 13

02D0 06B8 RIO_QUEUE14_RXDMA_CP Queue Receive DMA Completion Pointer Register 14

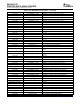

02D0 06BC RIO_QUEUE15_RXDMA_CP Queue Receive DMA Completion Pointer Register 15

02D0 06C0 - 02D0 006FC - Reserved

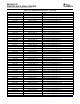

02D0 0700 RIO_TX_QUEUE_TEAR_DOWN Transmit Queue Teardown Register

02D0 0704 RIO_TX_CPPI_FLOW_MASKS0 Transmit CPPI Supported Flow Mask Register 0

02D0 0708 RIO_TX_CPPI_FLOW_MASKS1 Transmit CPPI Supported Flow Mask Register 1

02D0 070C RIO_TX_CPPI_FLOW_MASKS2 Transmit CPPI Supported Flow Mask Register 2

02D0 0710 RIO_TX_CPPI_FLOW_MASKS3 Transmit CPPI Supported Flow Mask Register 3

02D0 0714 RIO_TX_CPPI_FLOW_MASKS4 Transmit CPPI Supported Flow Mask Register 4

02D0 0718 RIO_TX_CPPI_FLOW_MASKS5 Transmit CPPI Supported Flow Mask Register 5

02D0 071C RIO_TX_CPPI_FLOW_MASKS6 Transmit CPPI Supported Flow Mask Register 6

02D0 0720 RIO_TX_CPPI_FLOW_MASKS7 Transmit CPPI Supported Flow Mask Register 7

02D0 0724 - 02D0 073C - Reserved

02D0 0740 RIO_RX_QUEUE_TEAR_DOWN Receive Queue Teardown Register

02D0 0744 RIO_RX_CPPI_CNTL Receive CPPI Control Register

02D0 0748 - 02D0 07DC - Reserved

02D0 07E0 RIO_TX_QUEUE_CNTL0 Transmit CPPI Weighted Round Robin Control Register 0

02D0 07E4 RIO_TX_QUEUE_CNTL1 Transmit CPPI Weighted Round Robin Control Register 1

02D0 07E8 RIO_TX_QUEUE_CNTL2 Transmit CPPI Weighted Round Robin Control Register 2

02D0 07EC RIO_TX_QUEUE_CNTL3 Transmit CPPI Weighted Round Robin Control Register 3

Submit Documentation Feedback C64x+ Peripheral Information and Electrical Specifications 239