Car Stereo System - Car Radio Digital Signal Processor User Manual

www.ti.com

7.14.2 EMAC Peripheral Register Description(s)

SM320C6455-EP

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS462B – SEPTEMBER 2007 – REVISED JANUARY 2008

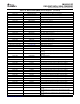

Table 7-71. Ethernet MAC (EMAC) Control Registers

HEX ADDRESS RANGE ACRONYM REGISTER NAME

02C8 0000 TXIDVER Transmit Identification and Version Register

02C8 0004 TXCONTROL Transmit Control Register

02C8 0008 TXTEARDOWN Transmit Teardown Register

02C8 000F - Reserved

02C8 0010 RXIDVER Receive Identification and Version Register

02C8 0014 RXCONTROL Receive Control Register

02C8 0018 RXTEARDOWN Receive Teardown Register

02C8 001C - Reserved

02C8 0020 - 02C8 007C - Reserved

02C8 0080 TXINTSTATRAW Transmit Interrupt Status (Unmasked) Register

02C8 0084 TXINTSTATMASKED Transmit Interrupt Status (Masked) Register

02C8 0088 TXINTMASKSET Transmit Interrupt Mask Set Register

02C8 008C TXINTMASKCLEAR Transmit Interrupt Mask Clear Register

02C8 0090 MACINVECTOR MAC Input Vector Register

02C8 0194 - 02C8 019C - Reserved

02C8 01A0 RXINTSTATRAW Receive Interrupt Status (Unmasked) Register

01C8 01A4 RXINTSTATMASKED Receive Interrupt Status (Masked) Register

01C8 01A8 RXINTMASKSET Receive Interrupt Mask Set Register

01C8 01AC RXINTMASKCLEAR Receive Interrupt Mask Clear Register

01C8 01B0 MACINTSTATRAW MAC Interrupt Status (Unmasked) Register

01C8 01B4 MACINTSTATMASKED MAC Interrupt Status (Masked) Register

01C8 01B8 MACINTMASKSET MAC Interrupt Mask Set Register

01C8 01BC MACINTMASKCLEAR MAC Interrupt Mask Clear Register

02C8 00C0 - 02C8 00FC - Reserved

02C8 0100 RXMBPENABLE Receive Multicast/Broadcast/Promiscuous Channel Enable Register

02C8 0104 RXUNICASTSET Receive Unicast Enable Set Register

02C8 0108 RXUNICASTCLEAR Receive Unicast Clear Register

02C8 010C RXMAXLEN Receive Maximum Length Register

02C8 0110 RXBUFFEROFFSET Receive Buffer Offset Register

02C8 0114 RXFILTERLOWTHRESH Receive Filter Low Priority Frame Threshold Register

02C8 0118 - 02C8 011C - Reserved

02C8 0120 RX0FLOWTHRESH Receive Channel 0 Flow Control Threshold Register

02C8 0124 RX1FLOWTHRESH Receive Channel 1 Flow Control Threshold Register

02C8 0128 RX2FLOWTHRESH Receive Channel 2 Flow Control Threshold Register

02C8 012C RX3FLOWTHRESH Receive Channel 3 Flow Control Threshold Register

02C8 0130 RX4FLOWTHRESH Receive Channel 4 Flow Control Threshold Register

02C8 0134 RX5FLOWTHRESH Receive Channel 5 Flow Control Threshold Register

02C8 0138 RX6FLOWTHRESH Receive Channel 6 Flow Control Threshold Register

02C8 013C RX7FLOWTHRESH Receive Channel 7 Flow Control Threshold Register

02C8 0140 RX0FREEBUFFER Receive Channel 0 Free Buffer Count Register

02C8 0144 RX1FREEBUFFER Receive Channel 1 Free Buffer Count Register

02C8 0148 RX2FREEBUFFER Receive Channel 2 Free Buffer Count Register

02C8 014C RX3FREEBUFFER Receive Channel 3 Free Buffer Count Register

02C8 0150 RX4FREEBUFFER Receive Channel 4 Free Buffer Count Register

02C8 0154 RX5FREEBUFFER Receive Channel 5 Free Buffer Count Register

C64x+ Peripheral Information and Electrical Specifications204 Submit Documentation Feedback