Car Stereo System - Car Radio Digital Signal Processor User Manual

www.ti.com

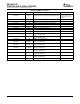

Bit(n-1) (n-2) (n-3)

Bit 0 Bit(n-1) (n-2) (n-3)

14

12

11

10

9

3

3

2

8

7

6

5

4

4

3

1

3

2

CLKS

CLKR

FSR (int)

FSR (ext)

DR

CLKX

FSX (int)

FSX (ext)

FSX (XDATDLY=00b)

DX

13

(A)

13

(A)

2

1

CLKS

FSR external

CLKR/X (no need to resync)

CLKR/X (needs resync)

SM320C6455-EP

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS462B – SEPTEMBER 2007 – REVISED JANUARY 2008

A. Parameter No. 13 applies to the first data bit only when XDATDLY ≠ 0.

B. The CLKS signal is shared by both McBSP0 and McBSP1 on this device.

Figure 7-52. McBSP Timing

(B)

Table 7-61. Timing Requirements for FSR When GSYNC = 1 (see Figure 7-53 )

-720

-850

A-1000/-1000

NO. UNIT

-1200

MIN MAX

1 t

su(FRH-CKSH)

Setup time, FSR high before CLKS high 4 ns

2 t

h(CKSH-FRH)

Hold time, FSR high after CLKS high 4 ns

Figure 7-53. FSR Timing When GSYNC = 1

Submit Documentation Feedback C64x+ Peripheral Information and Electrical Specifications 195