Car Stereo System - Car Radio Digital Signal Processor User Manual

www.ti.com

7.4.3 EDMA3 Peripheral Register Description(s)

SM320C6455-EP

FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS462B – SEPTEMBER 2007 – REVISED JANUARY 2008

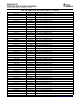

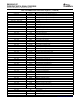

Table 7-3. C6455 EDMA3 Channel Synchronization Events (continued)

EDMA

BINARY EVENT NAME EVENT DESCRIPTION

CHANNEL

18-19 - - None

20 001 0100 INTDST1 RapidIO Interrupt 1

21-27 - - None

28 001 1100 VCP2REVT VCP2 receive event

29 001 1101 VCP2XEVT VCP2 transmit event

30 001 1110 TCP2REVT TCP2 receive event

31 001 1111 TCP2XEVT TCP2 transmit event

32 010 0000 UREVT UTOPIA receive event

33-39 - - None

40 010 1000 UXEVT UTOPIA transmit event

41-43 - - None

44 010 1100 ICREVT I2C receive event

45 010 1101 ICXEVT I2C transmit event

46-47 - - None

48 011 0000 GPINT0 GPIO event 0

49 011 0001 GPINT1 GPIO event 1

50 011 0010 GPINT2 GPIO event 2

51 011 0011 GPINT3 GPIO event 3

52 011 0100 GPINT4 GPIO event 4

53 011 0101 GPINT5 GPIO event 5

54 011 0110 GPINT6 GPIO event 6

55 011 0111 GPINT7 GPIO event 7

56 011 1000 GPINT8 GPIO event 8

57 011 1001 GPINT9 GPIO event 9

58 011 1010 GPINT10 GPIO event 10

59 011 1011 GPINT11 GPIO event 11

60 011 1100 GPINT12 GPIO event 12

61 011 1101 GPINT13 GPIO event 13

62 011 1110 GPINT14 GPIO event 14

63 011 1111 GPINT15 GPIO event 15

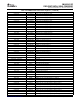

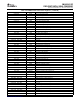

Table 7-4. EDMA3 Channel Controller Registers

HEX ADDRESS RANGE ACRONYM REGISTER NAME

02A0 0000 PID Peripheral ID Register

02A0 0004 CCCFG EDMA3CC Configuration Register

02A0 0008 - 02A0 00FC - Reserved

02A0 0100 DCHMAP0 DMA Channel 0 Mapping Register

02A0 0104 DCHMAP1 DMA Channel 1 Mapping Register

02A0 0108 DCHMAP2 DMA Channel 2 Mapping Register

02A0 010C DCHMAP3 DMA Channel 3 Mapping Register

02A0 0110 DCHMAP4 DMA Channel 4 Mapping Register

02A0 0114 DCHMAP5 DMA Channel 5 Mapping Register

02A0 0118 DCHMAP6 DMA Channel 6 Mapping Register

02A0 011C DCHMAP7 DMA Channel 7 Mapping Register

Submit Documentation Feedback C64x+ Peripheral Information and Electrical Specifications 111