Datasheet

Table Of Contents

0 10 20 30 40

-1.5

-1

-0.5

0

0.5

1

1.5

TIME (ns)

LATCH PIN

V

OUT

R

L

= 100:

4

1

3

2

0

V

OUT

(V)

LATCH

(

V

)

0 10 20 30 40

-1.5

-1

-0.5

0

0.5

1

1.5

TIME (ns)

LATCH PIN

V

OUT

R

L

= 100:

4

1

3

2

0

V

OUT

(V)

LATCH

(

V

)

1

10 100 1000

FREQUENCY (MHz)

-90

-80

-70

-60

-50

-40

-30

CROSSTALK (dBc)

P

IN

= -10 dBm

LOAD = 200:

MAX GAIN

LATCH

GAIN 1

0 10 20 30 40 50 60 70 80 90 100

-40

-30

-20

-10

0

10

20

30

40

DIFFERENTIAL OUTPUT (mV)

TIME (ns)

0

3

GAIN CONTROL SIGNALS

(

V

)

LATCH = 3.3V

PINS 9, 10, 11,12

50

100 150 200 250 300 350 400 450

FREQUENCY (MHz)

-50

0

50

100

150

200

250

300

350

INPUT IMPEDANCE (:)

|Z|

R

jX

0 10 20 30 40 50 60 70 80 90 100

-40

-30

-20

-10

0

10

20

30

40

DIFFERENTIAL OUTPUT (mV)

TIME (ns)

0

3

GAIN CONTROL SIGNALS

(

V

)

LATCH = 0

PINS 9, 10, 11,12

LMH6514

www.ti.com

SNOSB06A –JANUARY 2008–REVISED MARCH 2013

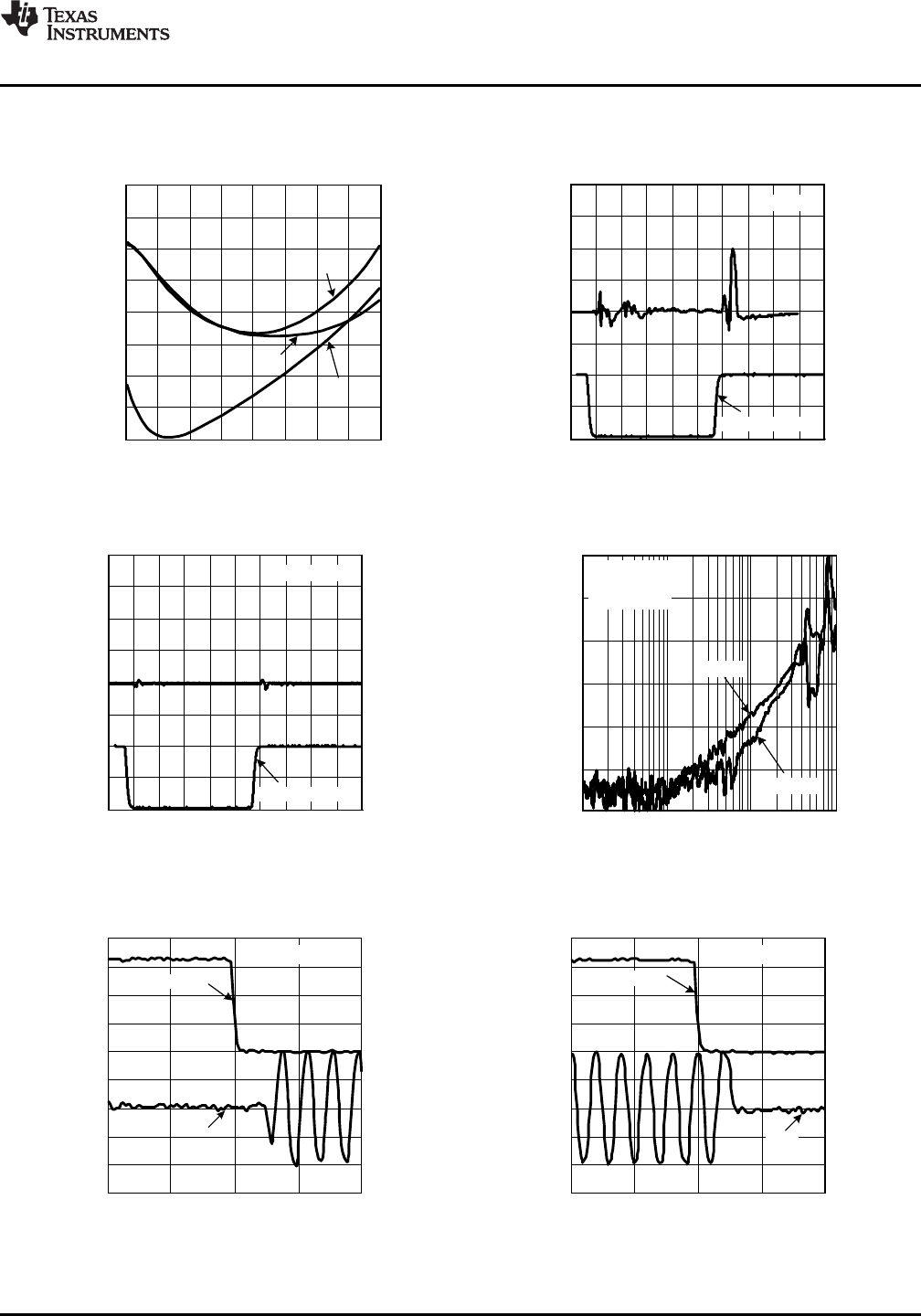

Typical Performance Characteristics

V

CC

= 5V (continued)

Output Impedance (S22) at

Maximum Gain High Gain Mode Digital Crosstalk

Figure 26. Figure 27.

Digital Crosstalk Digital Pin to Output Isolation

Figure 28. Figure 29.

Minimum Gain to Maximum Gain Switching Maximum Gain to Minimum Gain Switching

Using Latch Pin Using Latch Pin

Figure 30. Figure 31.

Copyright © 2008–2013, Texas Instruments Incorporated Submit Documentation Feedback 11

Product Folder Links: LMH6514