Datasheet

Table Of Contents

- Features

- Applications

- Key Specifications

- Description

- Absolute Maximum Ratings

- Operating Ratings

- Temperature-to-Digital Converter Characteristics

- Logic Electrical Characteristics

- DIGITAL DC CHARACTERISTICS

- SMBus DIGITAL SWITCHING CHARACTERISTICS

- Functional Description

- LM86 REGISTERS

- COMMAND REGISTER

- LOCAL and REMOTE TEMPERATURE REGISTERS (LT, RTHB, RTLB)

- STATUS REGISTER (SR)

- CONFIGURATION REGISTER

- CONVERSION RATE REGISTER

- LOCAL and REMOTE HIGH SETPOINT REGISTERS (LHS, RHSHB, and RHSLB)

- LOCAL and REMOTE LOW SETPOINT REGISTERS (LLS, RLSHB, and RLSLB)

- REMOTE TEMPERATURE OFFSET REGISTERS (RTOHB and RTOLB)

- LOCAL and REMOTE T_CRIT REGISTERS (RCS and LCS)

- T_CRIT HYSTERESIS REGISTER (TH)

- FILTER and ALERT CONFIGURE REGISTER

- MANUFACTURERS ID REGISTER

- DIE REVISION CODE REGISTER

- APPLICATION HINTS

- Data Sheet Revision History

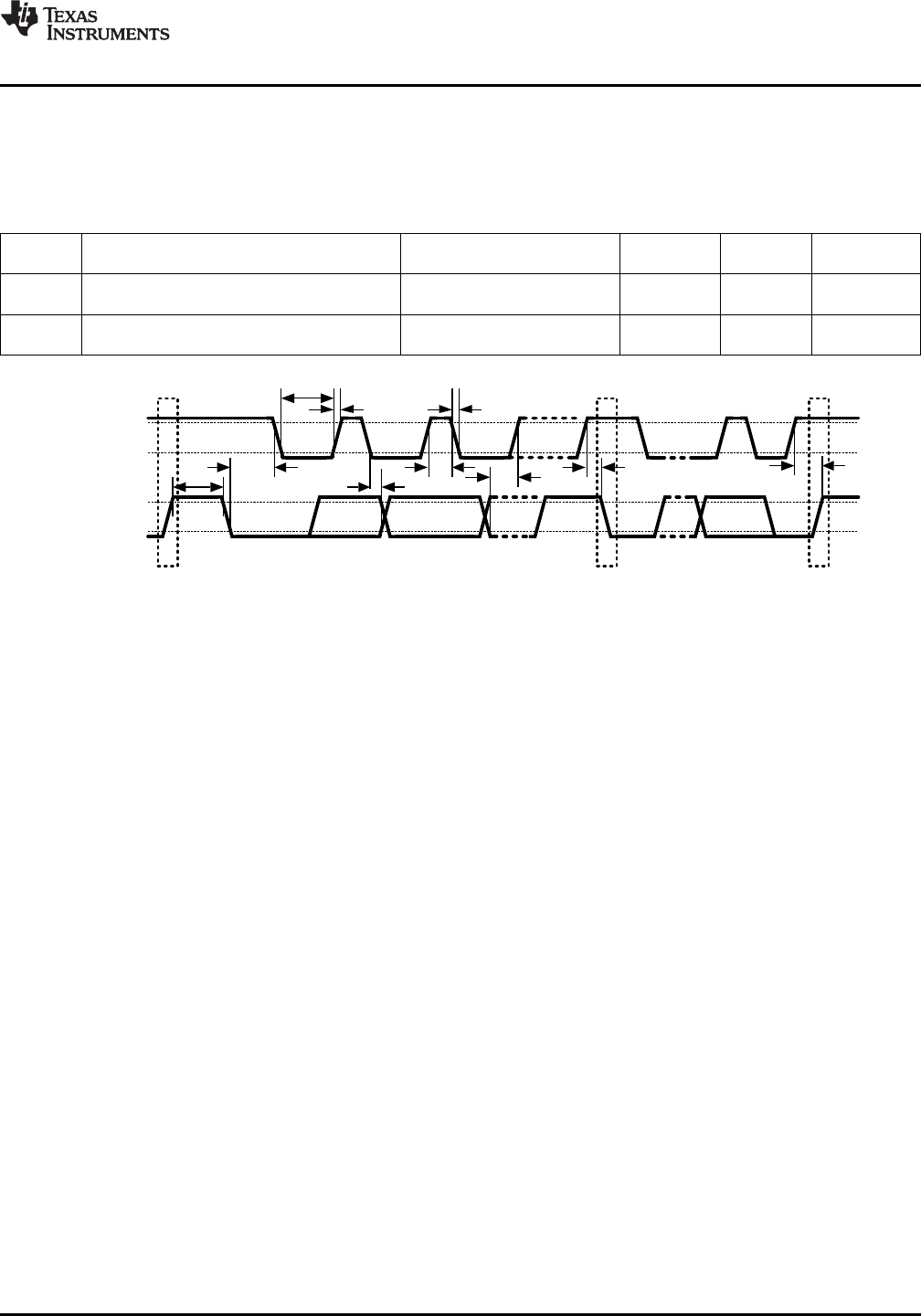

V

IH

V

IL

SMBCLK

P

S

V

IH

V

I

L

SMBDAT

t

BUF

t

HD;STA

t

LOW

t

R

t

HD;DAT

t

HIGH

t

F

t

SU;DAT

t

SU;STA

t

SU;STO

P

LM86

www.ti.com

SNIS114E –DECEMBER 2001–REVISED MARCH 2013

SMBus DIGITAL SWITCHING CHARACTERISTICS (continued)

Unless otherwise noted, these specifications apply for V

DD

=+3.0 Vdc to +3.6 Vdc, C

L

(load capacitance) on output lines = 80

pF. Boldface limits apply for T

A

= T

J

= T

MIN

to T

MAX

; all other limits T

A

= T

J

= +25°C, unless otherwise noted.

The switching characteristics of the LM86 fully meet or exceed the published specifications of the SMBus version 2.0. The

following parameters are the timing relationships between SMBCLK and SMBData signals related to the LM86. They adhere

to but are not necessarily the SMBus bus specifications.

Typical

(1)

Limits

(2)

Unit

Symbol Parameter Test Conditions

(Limit)

t

SU;STA

SMBus Repeated Start-Condition Setup Time, 0.6 µs (min)

SMBCLK High to SMBData Low

t

BUF

SMBus Free Time Between Stop and Start 1.3 µs (min)

Conditions

Figure 2. SMBus Communication

Copyright © 2001–2013, Texas Instruments Incorporated Submit Documentation Feedback 7

Product Folder Links: LM86