Datasheet

Table Of Contents

- Features

- Applications

- Key Specifications

- Description

- Absolute Maximum Ratings

- Operating Ratings

- Temperature-to-Digital Converter Characteristics

- Logic Electrical Characteristics

- DIGITAL DC CHARACTERISTICS

- SMBus DIGITAL SWITCHING CHARACTERISTICS

- Functional Description

- LM86 REGISTERS

- COMMAND REGISTER

- LOCAL and REMOTE TEMPERATURE REGISTERS (LT, RTHB, RTLB)

- STATUS REGISTER (SR)

- CONFIGURATION REGISTER

- CONVERSION RATE REGISTER

- LOCAL and REMOTE HIGH SETPOINT REGISTERS (LHS, RHSHB, and RHSLB)

- LOCAL and REMOTE LOW SETPOINT REGISTERS (LLS, RLSHB, and RLSLB)

- REMOTE TEMPERATURE OFFSET REGISTERS (RTOHB and RTOLB)

- LOCAL and REMOTE T_CRIT REGISTERS (RCS and LCS)

- T_CRIT HYSTERESIS REGISTER (TH)

- FILTER and ALERT CONFIGURE REGISTER

- MANUFACTURERS ID REGISTER

- DIE REVISION CODE REGISTER

- APPLICATION HINTS

- Data Sheet Revision History

-0.4

-0.35

-0.3

-0.25

-0.2

-0.15

-0.1

-0.05

0.05

0.1

0.15

0.2

0.25

0.3

0.35

0.4

-60 -40 -20 0 20 40 60 80

TEMPERATURE (

o

C)

0

TEMPERATURE SHIFT (

o

C)

100 120 140

n_ideality =1.008

using LM84.

n_ideality =1.0045

using LM84.

-6

-4

-2

0

2

4

6

8

10

12

14

-60 -40 -20 0 20 40 60 80 100 120 140

TEMPERATURE (

o

C)

ERROR (

o

C)

Pentium 4

Pentium III CPUID 68h/Celeron

Pentium 4

Pentium II

n_ideality =1.008

using LM84.

n_ideality =1.008

using LM86.

n_ideality =1.0045

using LM84.

TEMPERATURE (°C)

TEMPERATURE SHIFT (°C)

-1

-0.8

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

-60 -40 -20 0 20 40 60 80 100 120 140

LM86

SNIS114E –DECEMBER 2001–REVISED MARCH 2013

www.ti.com

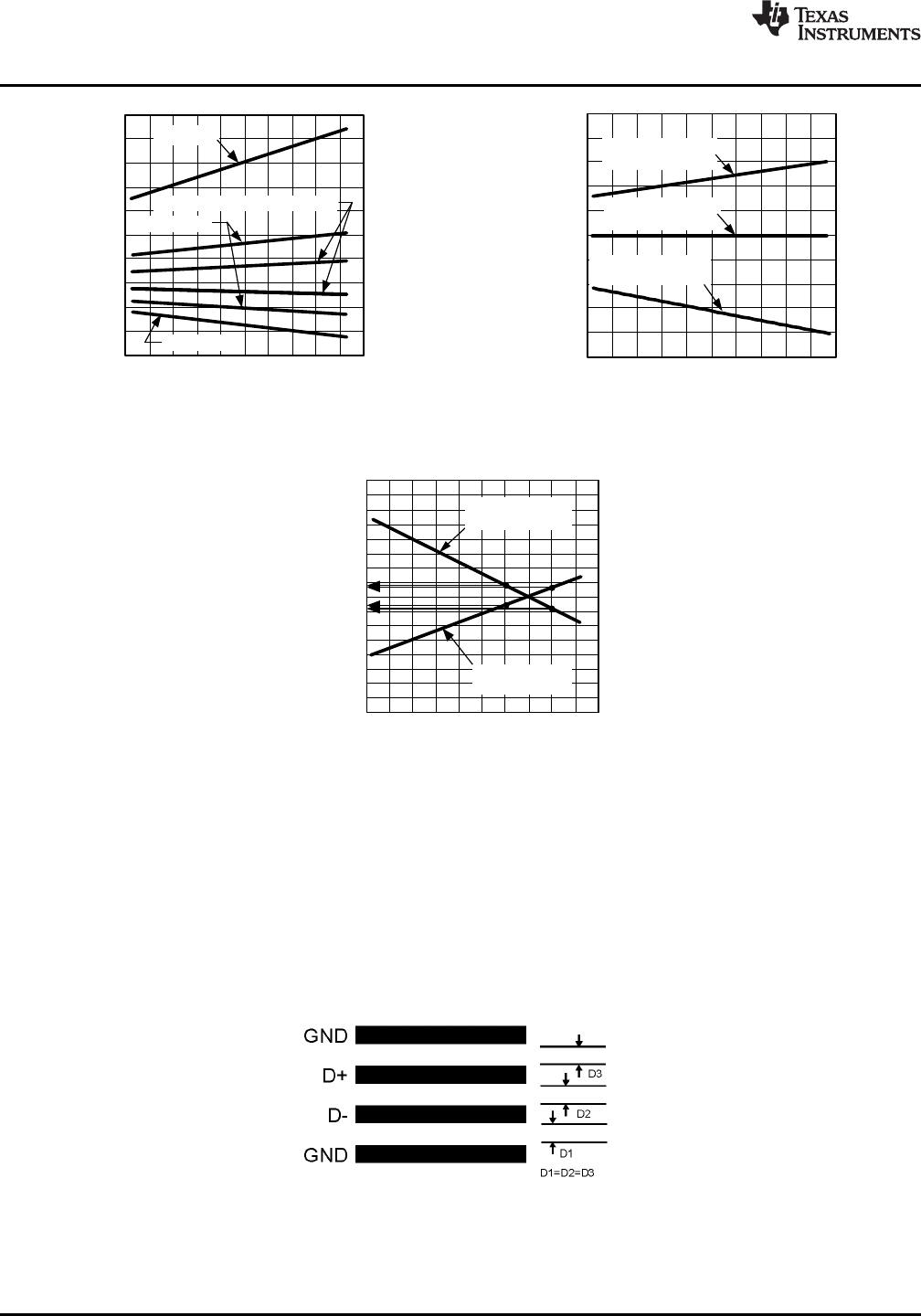

Figure 16. Error Caused by Nonideality Factor Figure 17. Errors Induced when Temperature

Sensor is Not Calibrated to Typical Nonideality

Figure 18. Compensating for an Untargeted Nonideality Factor

Temperature errors associated with nonideality may be reduced in a specific temperature range of concern

through use of the offset registers (11h and 12h). Figure 18 shows how the offset register may be used to

compensate for the nonideality errors shown in Figure 17. For the case of nonideality=1.008, the offset register

was set to −0.5°C resulting in the calculated residual error as shown in Figure 18. This offset has resulted in an

error of less than 0.05°C for the temperatures measured in the critical range between 60 to 100°C. This method

yields a first order correction factor.

Please send an email to hardware.monitor.team@nsc.com requesting further information on our recommended

setting of the offset register for different processor types.

PCB LAYOUT FOR MINIMIZING NOISE

Figure 19. Ideal Diode Trace Layout

24 Submit Documentation Feedback Copyright © 2001–2013, Texas Instruments Incorporated

Product Folder Links: LM86