Datasheet

Table Of Contents

- Features

- Applications

- Key Specifications

- Description

- Absolute Maximum Ratings

- Operating Ratings

- Temperature-to-Digital Converter Characteristics

- Logic Electrical Characteristics

- DIGITAL DC CHARACTERISTICS

- SMBus DIGITAL SWITCHING CHARACTERISTICS

- Functional Description

- LM86 REGISTERS

- COMMAND REGISTER

- LOCAL and REMOTE TEMPERATURE REGISTERS (LT, RTHB, RTLB)

- STATUS REGISTER (SR)

- CONFIGURATION REGISTER

- CONVERSION RATE REGISTER

- LOCAL and REMOTE HIGH SETPOINT REGISTERS (LHS, RHSHB, and RHSLB)

- LOCAL and REMOTE LOW SETPOINT REGISTERS (LLS, RLSHB, and RLSLB)

- REMOTE TEMPERATURE OFFSET REGISTERS (RTOHB and RTOLB)

- LOCAL and REMOTE T_CRIT REGISTERS (RCS and LCS)

- T_CRIT HYSTERESIS REGISTER (TH)

- FILTER and ALERT CONFIGURE REGISTER

- MANUFACTURERS ID REGISTER

- DIE REVISION CODE REGISTER

- APPLICATION HINTS

- Data Sheet Revision History

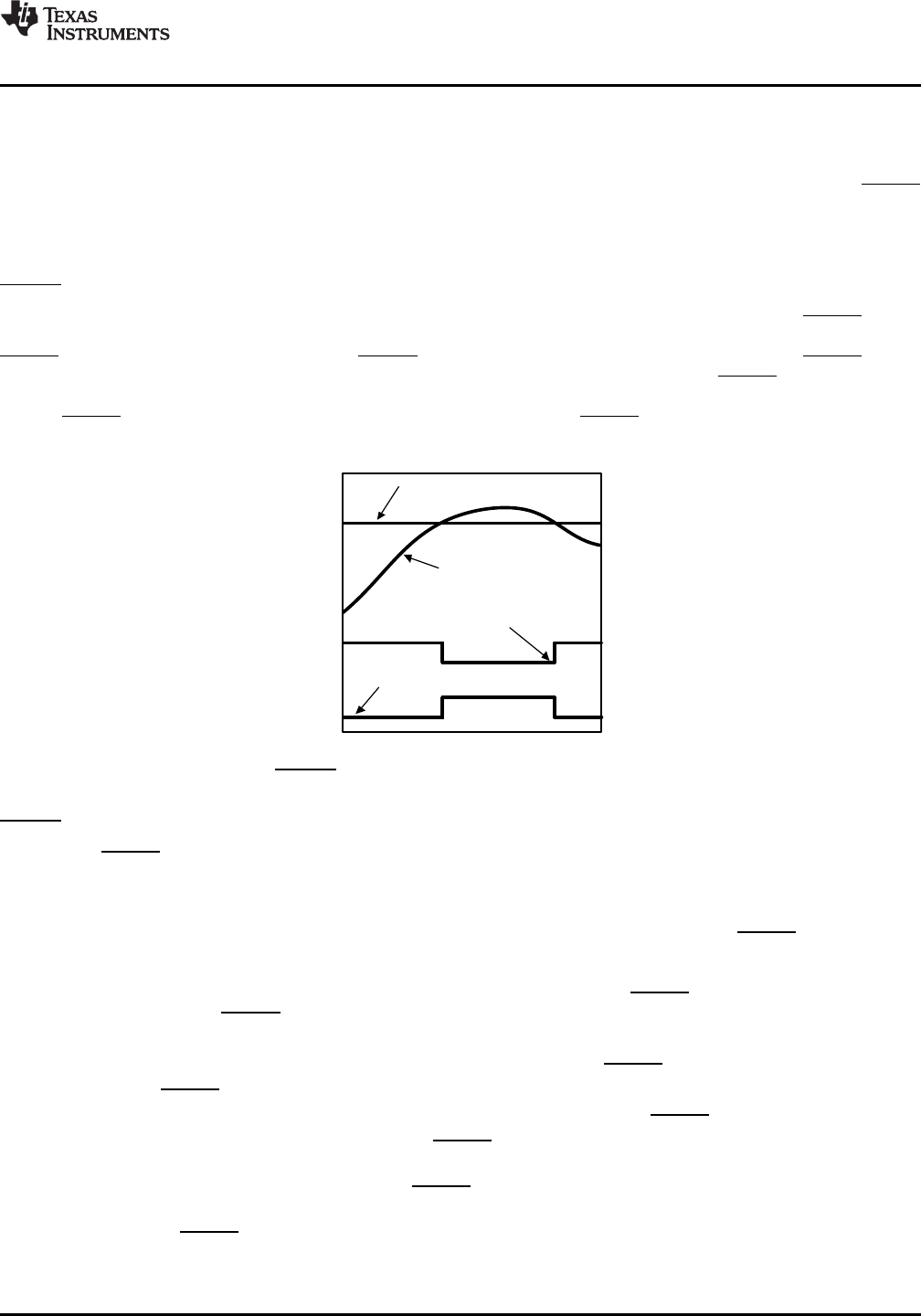

Remote High Limit

RDTS Measurement

LM86 ALERT Pin

Status Register: RTDS High

TIME

TEMPERATURE

LM86

www.ti.com

SNIS114E –DECEMBER 2001–REVISED MARCH 2013

Each temperature reading (LT and RT) is associated with a T_CRIT setpoint register (LCS, RCS), a HIGH

setpoint register (LHS and RHS) and a LOW setpoint register (LLS and RLS). At the end of every temperature

reading, a digital comparison determines whether that reading is above its HIGH or T_CRIT setpoint or below its

LOW setpoint. If so, the corresponding bit in the STATUS REGISTER is set. If the ALERT mask bit is not high,

any bit set in the STATUS REGISTER, with the exception of Busy (D7) and OPEN (D2), will cause the ALERT

output to be pulled low. Any temperature conversion that is out of the limits defined by the temperature setpoint

registers will trigger an ALERT. Additionally, the ALERT mask bit in the Configuration register must be cleared to

trigger an ALERT in all modes.

ALERT Output as a Temperature Comparator

When the LM86 is implemented in a system in which it is not serviced by an interrupt routine, the ALERT output

could be used as a temperature comparator. Under this method of use, once the condition that triggered the

ALERT to go low is no longer present, the ALERT is de-asserted (Figure 4). For example, if the ALERT output

was activated by the comparison of LT > LHS, when this condition is no longer true the ALERT will return HIGH.

This mode allows operation without software intervention, once all registers are configured during set-up. In order

for the ALERT to be used as a temperature comparator, bit D0 (the ALERT configure bit) in the FILTER and

ALERT CONFIGURE REGISTER (xBF) must be set high. This is not the power on default state.

Figure 4. ALERT Comparator Temperature Response Diagram

ALERT Output as an Interrupt

The LM86's ALERT output can be implemented as a simple interrupt signal when it is used to trigger an interrupt

service routine. In such systems it is undesirable for the interrupt flag to repeatedly trigger during or before the

interrupt service routine has been completed. Under this method of operation, during a read of the STATUS

REGISTER the LM86 will set the ALERT mask bit (D7 of the Configuration register) if any bit in the STATUS

REGISTER is set, with the exception of Busy (D7) and OPEN (D2). This prevents further ALERT triggering until

the master has reset the ALERT mask bit, at the end of the interrupt service routine. The STATUS REGISTER

bits are cleared only upon a read command from the master (see Figure 5) and will be re-asserted at the end of

the next conversion if the triggering condition(s) persist(s). In order for the ALERT to be used as a dedicated

interrupt signal, bit D0 (the ALERT configure bit) in the FILTER and ALERT CONFIGURE REGISTER (xBF) must

be set low. This is the power on default state.

The following sequence describes the response of a system that uses the ALERT output pin as a interrupt flag:

1. Master Senses ALERT low

2. Master reads the LM86 STATUS REGISTER to determine what caused the ALERT

3. LM86 clears STATUS REGISTER, resets the ALERT HIGH and sets the ALERT mask bit (D7 in the

Configuration register).

4. Master attends to conditions that caused the ALERT to be triggered. The fan is started, setpoint limits are

adjusted, etc.

5. Master resets the ALERT mask (D7 in the Configuration register).

Copyright © 2001–2013, Texas Instruments Incorporated Submit Documentation Feedback 9

Product Folder Links: LM86