Datasheet

Table Of Contents

- Features

- Applications

- Key Specifications

- Description

- Absolute Maximum Ratings

- Operating Ratings

- Temperature-to-Digital Converter Characteristics

- Logic Electrical Characteristics

- DIGITAL DC CHARACTERISTICS

- SMBus DIGITAL SWITCHING CHARACTERISTICS

- Functional Description

- LM86 REGISTERS

- COMMAND REGISTER

- LOCAL and REMOTE TEMPERATURE REGISTERS (LT, RTHB, RTLB)

- STATUS REGISTER (SR)

- CONFIGURATION REGISTER

- CONVERSION RATE REGISTER

- LOCAL and REMOTE HIGH SETPOINT REGISTERS (LHS, RHSHB, and RHSLB)

- LOCAL and REMOTE LOW SETPOINT REGISTERS (LLS, RLSHB, and RLSLB)

- REMOTE TEMPERATURE OFFSET REGISTERS (RTOHB and RTOLB)

- LOCAL and REMOTE T_CRIT REGISTERS (RCS and LCS)

- T_CRIT HYSTERESIS REGISTER (TH)

- FILTER and ALERT CONFIGURE REGISTER

- MANUFACTURERS ID REGISTER

- DIE REVISION CODE REGISTER

- APPLICATION HINTS

- Data Sheet Revision History

LM86

SNIS114E –DECEMBER 2001–REVISED MARCH 2013

www.ti.com

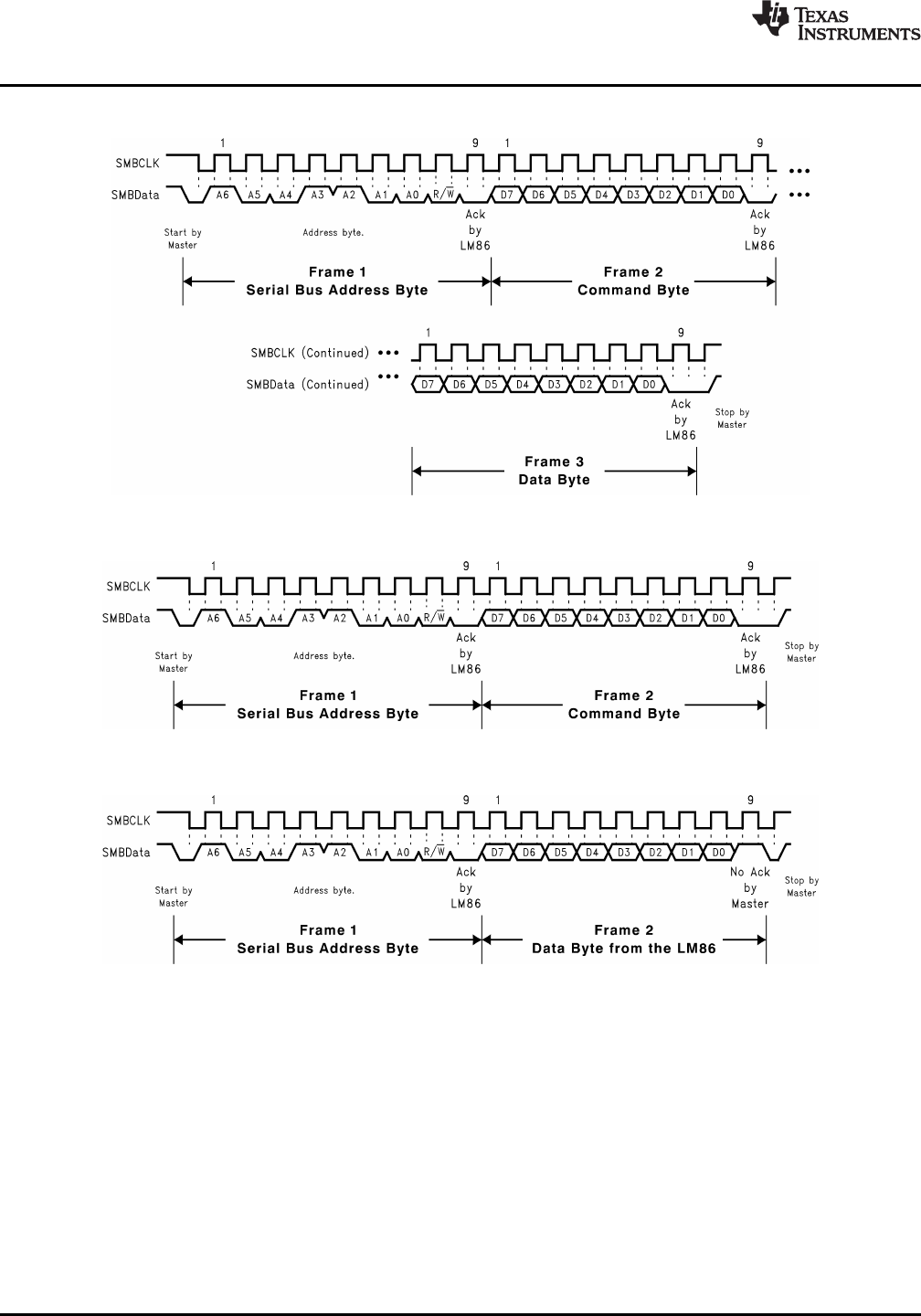

SMBus Timing Diagrams

Figure 8. (a) Serial Bus Write to the internal Command Register followed by a the Data Byte

Figure 9. (b) Serial Bus Write to the Internal Command Register

Figure 10. (c) Serial Bus Read from a Register with the Internal Command Register preset to desired

value

SERIAL INTERFACE RESET

In the event that the SMBus Master is RESET while the LM86 is transmitting on the SMBData line, the LM86

must be returned to a known state in the communication protocol. This may be done in one of two ways:

1. When SMBData is LOW, the LM86 SMBus state machine resets to the SMBus idle state if either SMBData

or SMBCLK are held low for more than 35ms (t

TIMEOUT

). Note that according to SMBus specification 2.0 all

devices are to timeout when either the SMBCLK or SMBData lines are held low for 25-35ms. Therefore, to

insure a timeout of all devices on the bus the SMBCLK or SMBData lines must be held low for at least 35ms.

2. When SMBData is HIGH, have the master initiate an SMBus start. The LM86 will respond properly to an

SMBus start condition at any point during the communication. After the start the LM86 will expect an SMBus

address byte.

14 Submit Documentation Feedback Copyright © 2001–2013, Texas Instruments Incorporated

Product Folder Links: LM86