Datasheet

DRV8825

www.ti.com

SLVSA73E –APRIL 2010–REVISED AUGUST 2013

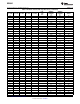

Table 3. Relative Current and Step Directions (continued)

FULL WINDING WINDING

ELECTRICAL

1/32 STEP 1/16 STEP 1/8 STEP 1/4 STEP 1/2 STEP STEP CURRENT CURRENT

ANGLE

70% A B

104 34% –94% 290

105 53 27 14 38% –92% 293

106 43% –90% 295

107 54 47% –88% 298

108 51% –86% 301

109 55 28 56% –83% 304

110 60% –80% 307

111 56 63% –77% 309

112 67% –74% 312

113 57 29 15 8 4 71% –71% 315

114 74% –67% 318

115 58 77% –63% 321

116 80% –60% 323

117 59 30 83% –56% 326

118 86% –51% 329

119 60 88% –47% 332

120 90% –43% 335

121 61 31 16 92% –38% 338

122 94% –34% 340

123 62 96% –29% 343

124 97% –24% 346

125 63 32 98% –20% 349

126 99% –15% 352

127 64 100% –10% 354

128 100% –5% 357

nRESET, nENBLE and nSLEEP Operation

The nRESET pin, when driven active low, resets internal logic, and resets the step table to the home position. It

also disables the H-bridge drivers. The STEP input is ignored while nRESET is active.

The nENBL pin is used to control the output drivers and enable/disable operation of the indexer. When nENBL is

low, the output H-bridges are enabled, and rising edges on the STEP pin are recognized. When nENBL is high,

the H-bridges are disabled, the outputs are in a high-impedance state, and the STEP input is ignored.

Driving nSLEEP low will put the device into a low power sleep state. In this state, the H-bridges are disabled, the

gate drive charge pump is stopped, the V3P3OUT regulator is disabled, and all internal clocks are stopped. In

this state all inputs are ignored until nSLEEP returns inactive high. When returning from sleep mode, some time

(approximately 1 ms) needs to pass before applying a STEP input, to allow the internal circuitry to stabilize. Note

that nRESET and nENABLE have internal pulldown resistors of approximately 100 kΩ. The nSLEEP pin has an

internal pulldown resistor of 1 MΩ. nSLEEP and nRESET signals need to be driven to logic high for device

operation.

Protection Circuits

The DRV8825 is fully protected against undervoltage, overcurrent and overtemperature events.

Copyright © 2010–2013, Texas Instruments Incorporated Submit Documentation Feedback 13

Product Folder Links: DRV8825