Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- DESCRIPTION

- PINOUT INFORMATION

- ABSOLUTE MAXIMUM RATINGS

- THERMAL INFORMATION

- RECOMMENDED OPERATING CONDITIONS

- ELECTRICAL CHARACTERISTICS

- TIMING REQUIREMENTS

- TYPICAL CHARACTERISTICS

- SYSTEM DIAGRAMS

- APPLICATION INFORMATION

- ECCENTRIC ROTATING MASS MOTORS (ERM)

- LINEAR RESONANCE ACTUATORS (LRA)

- AUTO-RESONANCE ENGINE FOR LRA

- OPEN LOOP OPERATION FOR LRA

- SMART LOOP ARCHITECTURE

- AUTO CALIBRATION

- WAVEFORM LIBRARIES

- WAVEFORM SEQUENCER

- LIBRARY PARAMETERIZATION

- REAL-TIME PLAYBACK (RTP) MODE

- MULTI-MODE INPUT PIN (IN/TRIG)

- DEVICE ENABLE

- CONSTANT VIBRATION STRENGTH

- EDGE RATE CONTROL

- CAPACITOR SELECTION

- MODES OF OPERATION

- BLOCK DIAGRAM

- GENERAL I2C OPERATION

- SINGLE-BYTE AND MULTIPLE-BYTE TRANSFERS

- SINGLE-BYTE WRITE

- MULTIPLE-BYTE WRITE AND INCREMENTAL MULTIPLE-BYTE WRITE

- SINGLE-BYTE READ

- MULTIPLE-BYTE READ

- REGISTER MAP

- DEVICE PROGRAMMING

- WAVEFORM LIBRARY EFFECTS LIST

- PCB LAYOUT RECOMMENDATIONS

- Revision History

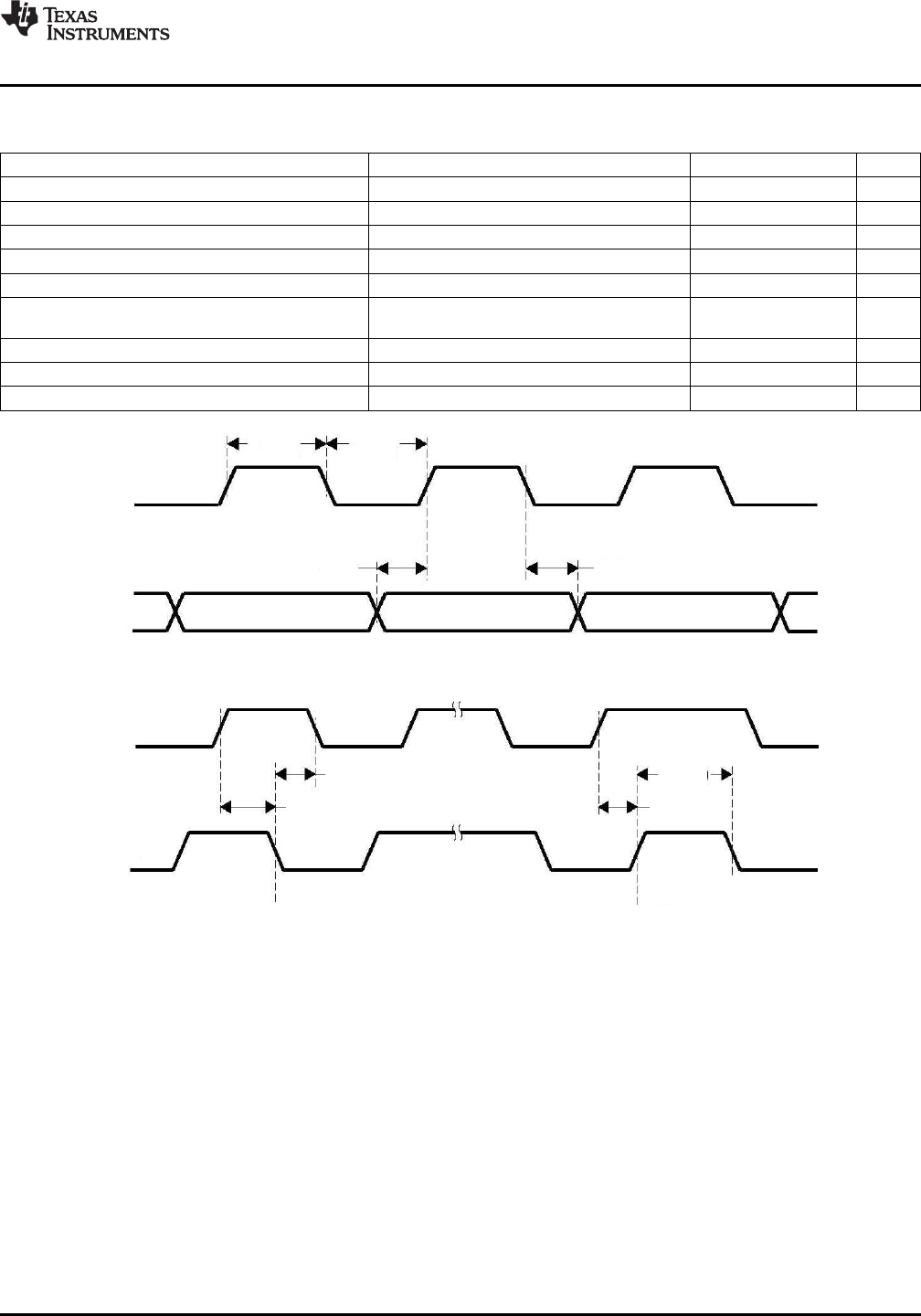

SCL

SDA

t

su2

t

h2

t

(buf)

t

su3

Start Condition Stop Condition

SCL

SDA

t (H)

w

t (L)

w

t

su1

t

h1

DRV2605

www.ti.com

SLOS825B –DECEMBER 2012–REVISED JANUARY 2014

TIMING REQUIREMENTS

T

A

= 25°C, VDD = 3.6 V (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

f

SCL

Frequency, SCL No wait states 400 kHz

t

W(H)

Pulse duration, SCL high 0.6 μs

t

W(L)

Pulse duration, SCL low 1.3 μs

t

SU1

Setup time, SDA to SCL 100 ns

t

H1

Hold time, SCL to SDA 10 ns

Bus free time between stop and start

t

(BUF)

1.3 μs

condition

t

SU2

Setup time, SCL to start condition 0.6 μs

t

H2

Hold time, start condition to SCL 0.6 μs

t

SU3

Setup time, SCL to stop condition 0.6 μs

Figure 1. SCL and SDA Timing

Figure 2. Timing for Start and Stop Conditions

Copyright © 2012–2014, Texas Instruments Incorporated Submit Documentation Feedback 5

Product Folder Links: DRV2605