Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- DESCRIPTION

- DEVICE INFORMATION

- ABSOLUTE MAXIMUM RATINGS

- THERMAL RESISTANCE FOR TSSOP (PW) PACKAGE

- RECOMMENDED OPERATING CONDITIONS

- RECOMMENDED CRYSTAL/VCXO SPECIFICATIONS

- EEPROM SPECIFICATION

- TIMING REQUIREMENTS

- DEVICE CHARACTERISTICS

- DEVICE CHARACTERISTICS (Continued)

- DEVICE CHARACTERISTICS (Continued)

- PARAMETER MEASUREMENT INFORMATION

- TYPICAL CHARACTERISTICS

- APPLICATION INFORMATION

- Control Terminal Configuration

- DEFAULT DEVICE SETTING

- SDA/SCL SERIAL INTERFACE

- DATA PROTOCOL

- Generic Programming Sequence

- Byte Write Programming Sequence

- Byte Read Programming Sequence

- Block Write Programming Sequence

- Block Read Programming Sequence

- Timing Diagram for the SDA/SCL Serial Control Interface

- SDA/SCL Hardware Interface

- SDA/SCL CONFIGURATION REGISTERS

- PLL MULTIPLIER/DIVIDER DEFINITIONPLL settings limits: 16≤q≤63, 0≤p≤7, 0≤r≤511 to PLL Multiplier/Divider Definition Section

- Revision History

10pF

1kW

LVCMOS

CDCE949

CDCEL949

1kW

LVCMOS LVCMOS

CDCE949

CDCEL949

TypicalDriver

Impedance

~32 W

LineImpedance

Zo=50 W

Series

Termination

~ 18 W

CDCE949

CDCEL949

www.ti.com

SCAS844D –AUGUST 2007–REVISED MARCH 2010

DEVICE CHARACTERISTICS (Continued)

over recommended operating free-air temperature range (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP

(1)

MAX UNIT

SAVE THIS CDCEL949 – LVCMOS PARAMETER FOR V

DDOUT

= 1.8 V – MODE

V

DDOUT

= 1.7 V, I

OH

= –0.1 mA 1.6

V

OH

LVCMOS high-level output voltage V

DDOUT

= 1.7 V, I

OH

= –4 mA 1.4 V

V

DDOUT

= 1.7 V, I

OH

= –8 mA 1.1

V

DDOUT

= 1.7 V, I

OL

= 0.1 mA 0.1

V

OL

LVCMOS low-level output voltage V

DDOUT

= 1.7 V, I

OL

= 4 mA 0.3 V

V

DDOUT

= 1.7 V, I

OL

= 8 mA 0.6

t

PLH

,

Propagation delay PLL bypass 2.6 ns

t

PHL

t

r

/t

f

Rise and fall time V

DDOUT

= 1.8 V (20%–80%) 0.7 ns

1 PLL switching, Y2-to-Y3 70 120 ps

t

jit(cc)

Cycle-to-cycle jitter

(2) (3)

4 PLLs switching, Y2-to-Y9 120 170

1 PLL switching, Y2-to-Y3 90 140 ps

t

jit(per)

Peak-to-peak period jitter

(2) (3)

4 PLLs switching, Y2-to-Y9 130 190

f

OUT

= 50 MHz; Y1-to-Y3 60 ps

t

sk(o)

Output skew

(4)

f

OUT

= 50 MHz; Y2-to-Y5 or Y6-to-Y9 160

odc Output duty cycle

(5)

f

VCO

= 100 MHz; Pdiv = 1 45 55 %

SDA/SCL PARAMETER

V

IK

SCL and SDA input clamp voltage V

DD

= 1.7 V; I

I

= –18 mA –1.2 V

I

IH

SCL and SDA input current V

I

= V

DD

; V

DD

= 1.9 V ±10 mA

V

IH

SDA/SCL input high voltage

(6)

0.7 V

DD

V

0.3

V

IL

SDA/SCL input low voltage

(6)

V

V

DD

0.2

V

OL

SDA low-level output voltage I

OL

= 3 mA, V

DD

= 1.7 V V

V

DD

C

I

SCL/SDA input capacitance V

I

= 0 V or V

DD

3 10 pF

(1) All typical values are at respective nominal V

DD

.

(2) 10000 cycles.

(3) Jitter depends on device configuration. Data is taken under the following conditions: 1-PLL: f

IN

= 27 MHz, Y2/3 = 27 MHz, (measured at

Y2), 4-PLL: f

IN

= 27 MHz, Y2/3 = 27 MHz, (measured at Y2), Y4/5 = 16.384 MHz, Y6/7 = 74.25 MHz, Y8/9 = 48 MHz.

(4) The t

sk(o)

specification is only valid for equal loading of each bank of outputs and outputs are generated from same divider; data

sampled on rising edge (t

r

).

(5) odc depends on output rise- and fall-time (t

r

/t

f

).

(6) SDA and SCL pins are 3.3-V tolerant.

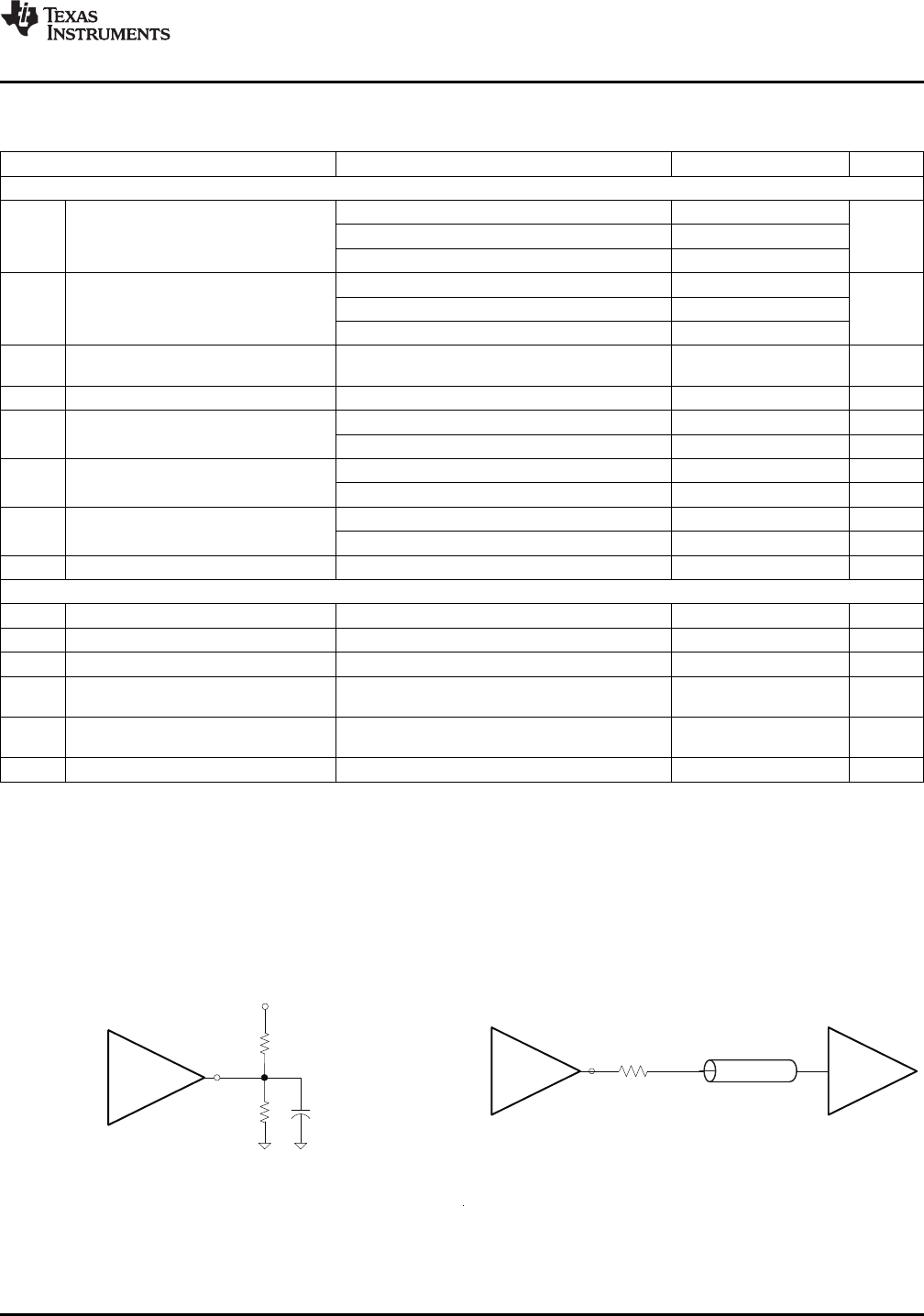

PARAMETER MEASUREMENT INFORMATION

Figure 1. Test Load Figure 2. Test Load for 50 Ω Board Environment

Copyright © 2007–2010, Texas Instruments Incorporated Submit Documentation Feedback 7

Product Folder Link(s): CDCE949 CDCEL949