Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- DESCRIPTION

- DEVICE INFORMATION

- ABSOLUTE MAXIMUM RATINGS

- THERMAL RESISTANCE FOR TSSOP (PW) PACKAGE

- RECOMMENDED OPERATING CONDITIONS

- RECOMMENDED CRYSTAL/VCXO SPECIFICATIONS

- EEPROM SPECIFICATION

- TIMING REQUIREMENTS

- DEVICE CHARACTERISTICS

- DEVICE CHARACTERISTICS (Continued)

- DEVICE CHARACTERISTICS (Continued)

- PARAMETER MEASUREMENT INFORMATION

- TYPICAL CHARACTERISTICS

- APPLICATION INFORMATION

- Control Terminal Configuration

- DEFAULT DEVICE SETTING

- SDA/SCL SERIAL INTERFACE

- DATA PROTOCOL

- Generic Programming Sequence

- Byte Write Programming Sequence

- Byte Read Programming Sequence

- Block Write Programming Sequence

- Block Read Programming Sequence

- Timing Diagram for the SDA/SCL Serial Control Interface

- SDA/SCL Hardware Interface

- SDA/SCL CONFIGURATION REGISTERS

- PLL MULTIPLIER/DIVIDER DEFINITIONPLL settings limits: 16≤q≤63, 0≤p≤7, 0≤r≤511 to PLL Multiplier/Divider Definition Section

- Revision History

CDCE949

CDCEL949

SCAS844D –AUGUST 2007–REVISED MARCH 2010

www.ti.com

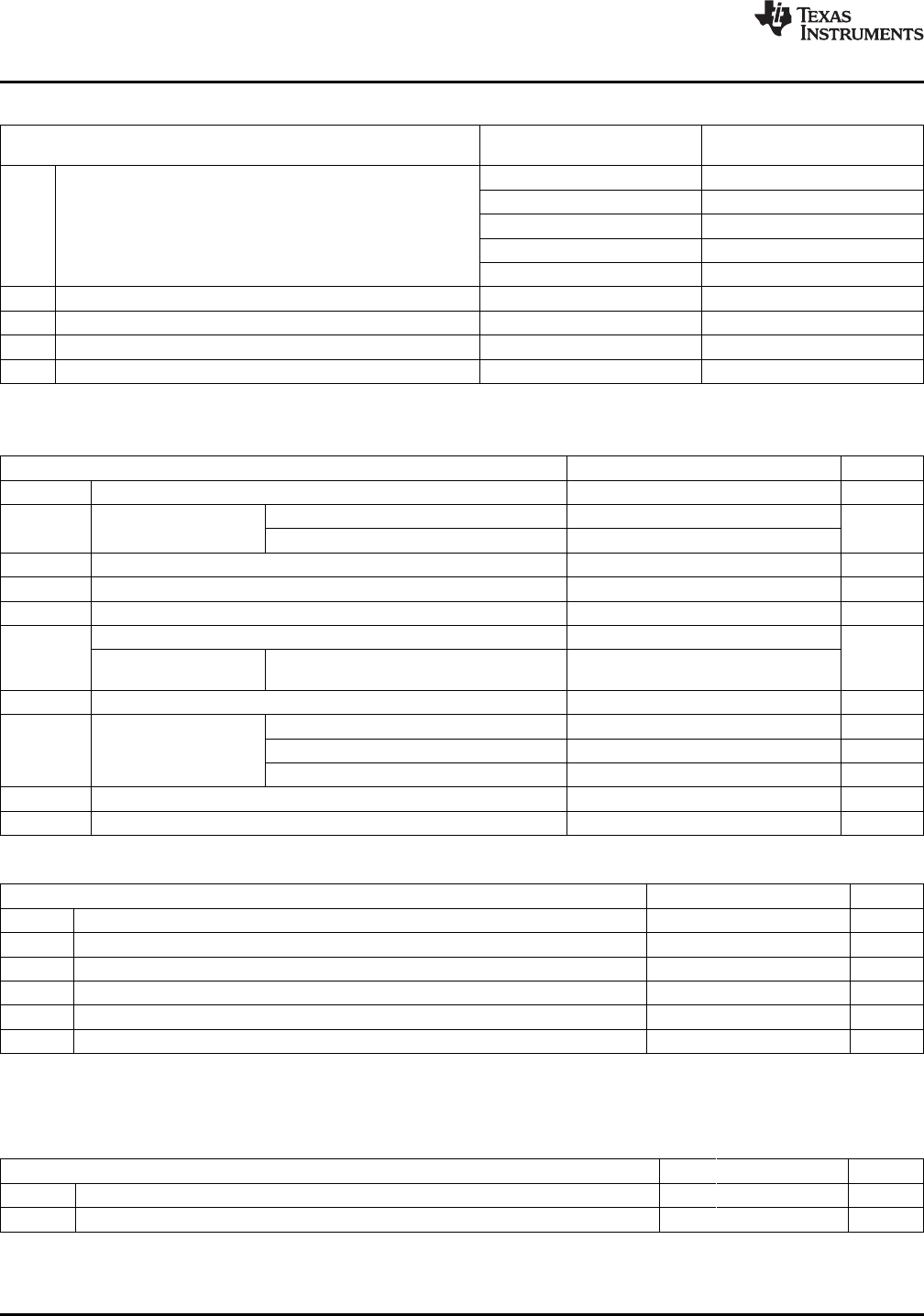

THERMAL RESISTANCE FOR TSSOP (PW) PACKAGE

(1)

AIRFLOW TSSOP24

PARAMETER

(lfm) °C/W

0 91

150 75

T

JA

Thermal Resistance Junction to Ambient 200 74

250 73

500 65

T

JC

Thermal Resistance Junction to Case — 27

T

JB

Thermal Resistance Junction to Board — 52

R

qJT

Thermal Resistance Junction to Top — 0.5

R

qJB

Thermal Resistance Junction to Bottom — 50

(1) The package thermal impedance is calculated in accordance with JESD 51 and JEDEC2S2P (high-k board).

RECOMMENDED OPERATING CONDITIONS

MIN NOM MAX UNIT

V

DD

Device supply voltage 1.7 1.8 1.9 V

CDCE949 2.3 3.6

Output Yx supply

V

DD(OUT)

V

voltage

CDCEL949 1.7 1.9

V

IL

Low level input voltage LVCMOS 0.3 × V

DD

V

V

IH

High level input voltage LVCMOS 0.7 × V

DD

V

V

I(thresh)

Input voltage threshold LVCMOS 0.5 × V

DD

V

Input voltage range S0 0 1.9

V

IS

V

Input voltage range S1, V

Ithresh

= 0.5 V

DD

0 3.6

S2, SDA, SCL

V

ICLK

Input voltage range CLK 0 1.9 V

V

DDout

= 3.3 V ±12 mA

I

OH

/I

OL

Output current V

DDout

= 2.5 V ±10 mA

V

DDout

= 1.8 V ±8 mA

C

L

Output load LVCMOS 10 pF

T

A

Operating free-air temperature –40 85 °C

RECOMMENDED CRYSTAL/VCXO SPECIFICATIONS

(1)

MIN NOM MAX UNIT

f

Xtal

Crystal Input frequency range (fundamental mode) 8 27 32 MHz

ESR Effective series resistance 100 Ω

f

PR

Pulling range (0 V ≤ V

Ctrl

≤ 1.8 V)

(2)

±120 ±150 ppm

V

(Ctrl)

Frequency control voltage 0 V

DD

V

C

0

/C

1

Pullability ratio 220

C

L

On-chip load capacitance at Xin and Xout 0 20 pF

(1) For more information about VCXO configuration and crystal recommendation see application report SCAA085.

(2) Pulling range depends on crystal type, on-chip crystal load capacitance and PCB stray capacitance; pulling range of min ±120 ppm

applies for crystal listed in the application report SCAA085.

EEPROM SPECIFICATION

MIN TYP MAX UNIT

EEcyc EEcyc programming cycles of EEPROM 1000 cycles

EEret EEret data retention 10 years

4 Submit Documentation Feedback Copyright © 2007–2010, Texas Instruments Incorporated

Product Folder Link(s): CDCE949 CDCEL949