Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- DESCRIPTION

- DEVICE INFORMATION

- ABSOLUTE MAXIMUM RATINGS

- THERMAL RESISTANCE FOR TSSOP (PW) PACKAGE

- RECOMMENDED OPERATING CONDITIONS

- RECOMMENDED CRYSTAL/VCXO SPECIFICATIONS

- EEPROM SPECIFICATION

- TIMING REQUIREMENTS

- DEVICE CHARACTERISTICS

- DEVICE CHARACTERISTICS (Continued)

- DEVICE CHARACTERISTICS (Continued)

- PARAMETER MEASUREMENT INFORMATION

- TYPICAL CHARACTERISTICS

- APPLICATION INFORMATION

- Control Terminal Configuration

- DEFAULT DEVICE SETTING

- SDA/SCL SERIAL INTERFACE

- DATA PROTOCOL

- Generic Programming Sequence

- Byte Write Programming Sequence

- Byte Read Programming Sequence

- Block Write Programming Sequence

- Block Read Programming Sequence

- Timing Diagram for the SDA/SCL Serial Control Interface

- SDA/SCL Hardware Interface

- SDA/SCL CONFIGURATION REGISTERS

- PLL MULTIPLIER/DIVIDER DEFINITIONPLL settings limits: 16≤q≤63, 0≤p≤7, 0≤r≤511 to PLL Multiplier/Divider Definition Section

- Revision History

CDCE949

CDCEL949

SCAS844D –AUGUST 2007–REVISED MARCH 2010

www.ti.com

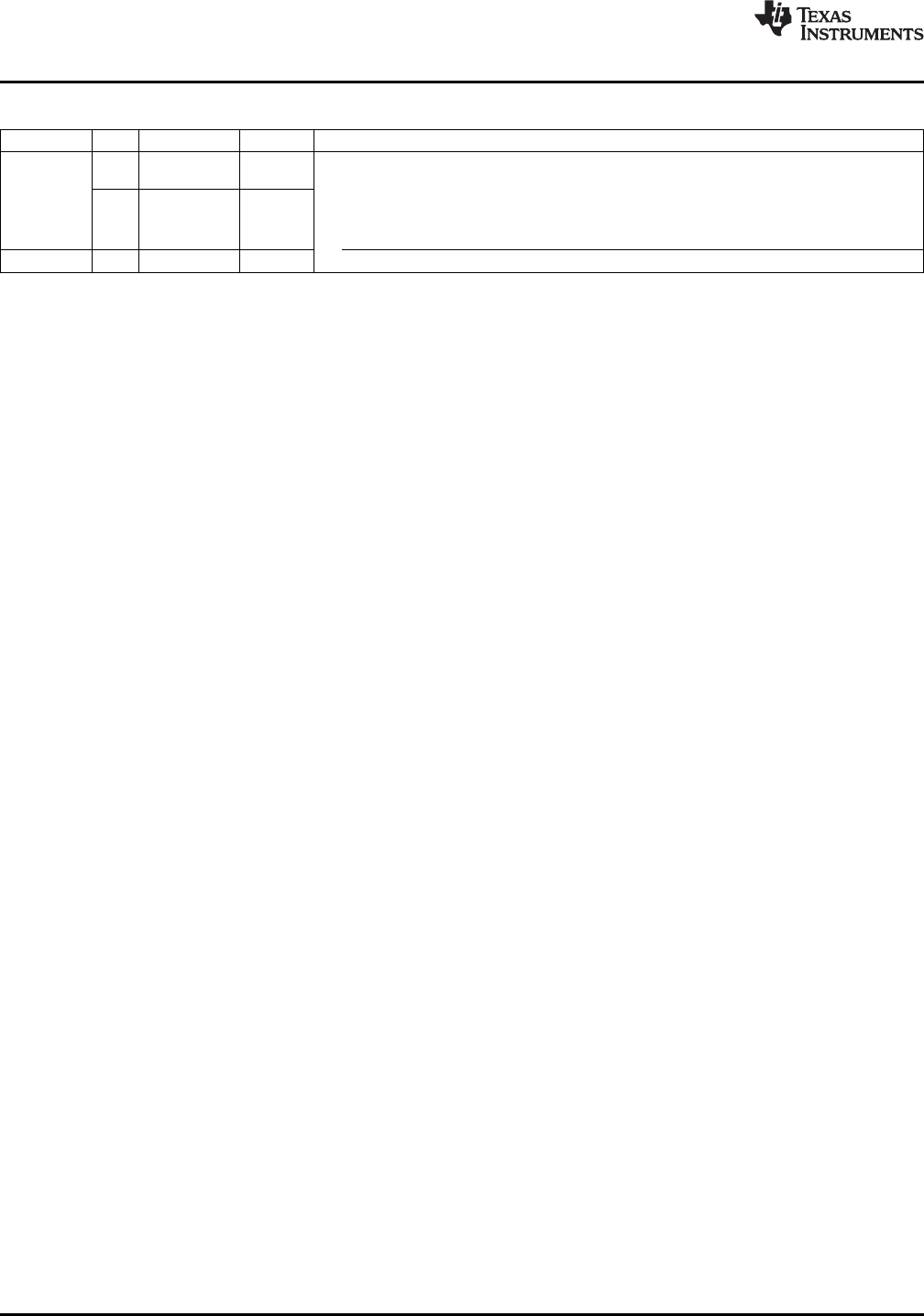

Table 9. Generic Configuration Register (continued)

OFFSET

(1)

Bit

(2)

Acronym Default

(3)

DESCRIPTION

06h 7-Bit Byte Count (Defines the number of Bytes which will be sent from this device at the next Block Read

7:1 BCOUNT 50h

transfer; all bytes must be read out to correctly finish the read cycle.)

Initiate EEPROM Write Cycle

(4) (9)

0 EEWRITE 0b

0 – no EEPROM write cycle

1 – start EEPROM write cycle (internal configuration register is saved to the EEPROM)

07h-0Fh — — 0h Reserved – do not write others than 0

(9) NOTE: The EEPROM WRITE bit must be sent last. This ensures that the content of all internal registers are written into the EEPROM.

The EEWRITE cycle is initiated by the rising edge of the EEWRITE-Bit. A static level high does not trigger an EEPROM WRITE cycle.

The EEWRITE-Bit must be reset low after the programming is completed. The programming status can be monitored by readout EEPIP.

If EELOCK is set high, no EEPROM programming will be possible.

16 Submit Documentation Feedback Copyright © 2007–2010, Texas Instruments Incorporated

Product Folder Link(s): CDCE949 CDCEL949