Datasheet

Table Of Contents

- FEATURES

- APPLICATIONS

- DESCRIPTION

- DEVICE INFORMATION

- ABSOLUTE MAXIMUM RATINGS

- THERMAL RESISTANCE FOR TSSOP (PW) PACKAGE

- RECOMMENDED OPERATING CONDITIONS

- RECOMMENDED CRYSTAL/VCXO SPECIFICATIONS

- EEPROM SPECIFICATION

- TIMING REQUIREMENTS

- DEVICE CHARACTERISTICS

- DEVICE CHARACTERISTICS (Continued)

- DEVICE CHARACTERISTICS (Continued)

- PARAMETER MEASUREMENT INFORMATION

- TYPICAL CHARACTERISTICS

- APPLICATION INFORMATION

- Control Terminal Configuration

- DEFAULT DEVICE SETTING

- SDA/SCL SERIAL INTERFACE

- DATA PROTOCOL

- Generic Programming Sequence

- Byte Write Programming Sequence

- Byte Read Programming Sequence

- Block Write Programming Sequence

- Block Read Programming Sequence

- Timing Diagram for the SDA/SCL Serial Control Interface

- SDA/SCL Hardware Interface

- SDA/SCL CONFIGURATION REGISTERS

- PLL MULTIPLIER/DIVIDER DEFINITIONPLL settings limits: 16≤q≤63, 0≤p≤7, 0≤r≤511 to PLL Multiplier/Divider Definition Section

- Revision History

CDCE949

CDCEL949

SCAS844D –AUGUST 2007–REVISED MARCH 2010

www.ti.com

SDA/SCL CONFIGURATION REGISTERS

The clock input, control pins, PLLs and output stages are user configurable. The following tables and

explanations describe the programmable functions of the CDCE949/CDCEL949. All settings can be manually

written to the device via the SDA/SCL bus, or are easily programmable by using the TI Pro Clock software. TI

Pro Clock software allows the user to quickly make all settings and automatically calculates the values for

optimized performance at lowest jitter.

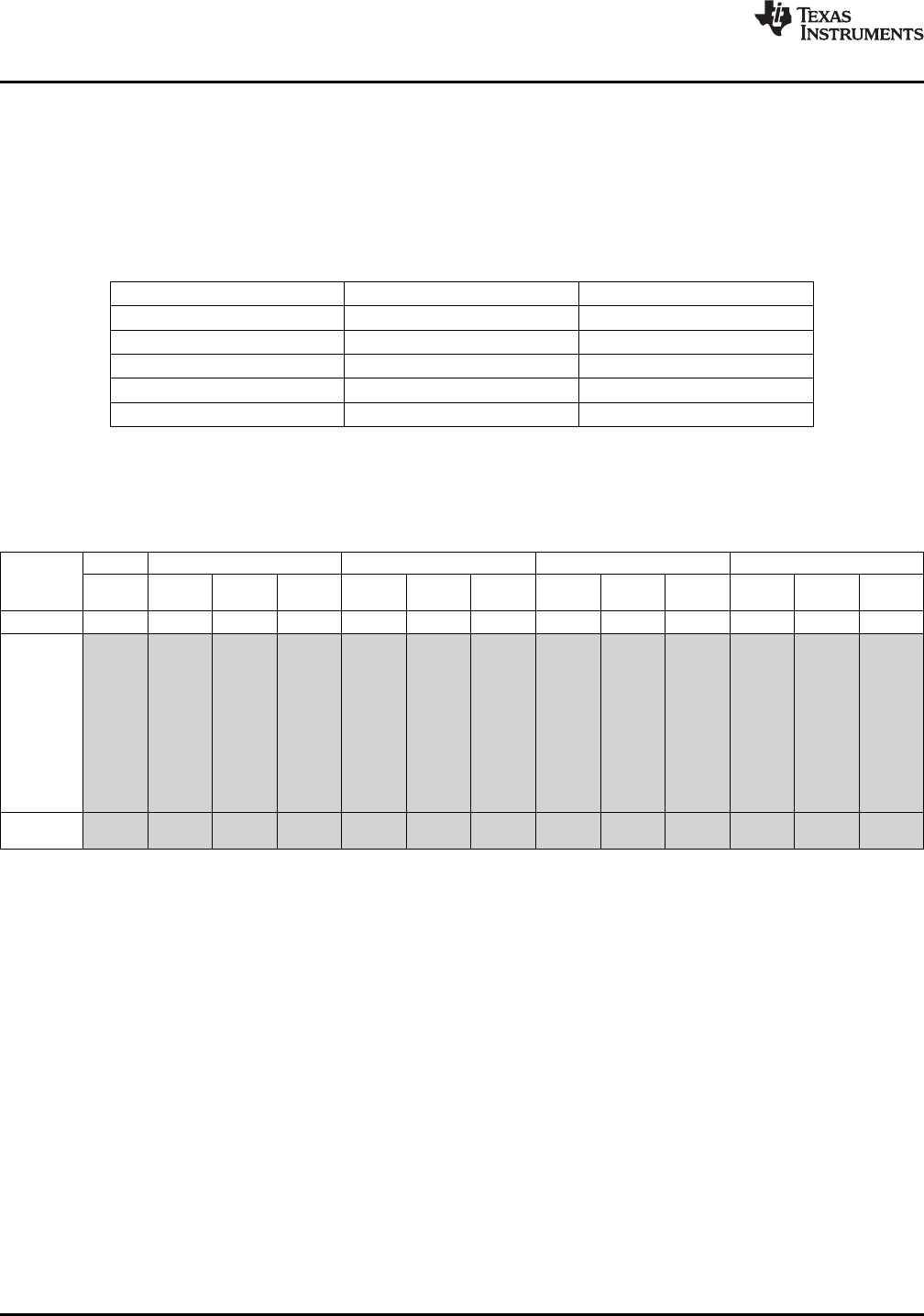

Table 7. SDA/SCL Registers

ADDRESS OFFSET REGISTER DESCRIPTION TABLE

00h Generic Configuration Register Table 9

10h PLL1 Configuration Register Table 10

20h PLL2 Configuration Register Table 11

30h PLL3 Configuration Register Table 12

40h PLL4 Configuration Register Table 13

The grey-highlighted Bits described in the Configuration Registers tables on the following pages, belong to the

Control Terminal Register. The user can predefine up to eight different control settings. These settings can then

be selected by the external control pins, S0, S1, and S2 (See the Control Terminal Configuration section).

Table 8. Configuration Register, External Control Terminals

Y1 PLL1 SETTING PLL2 SETTING PLL3 SETTING PLL4 SETTING

EXTERNAL

CONTROL

Output Freq. SSC Output Freq. SSC Output Freq. SSC Output Freq. SSC Output

PINS

Select Select Select Select Select Select Select Select Select Select Select Select Select

S2 S1 S0 Y1 FS1 SSC1 Y2Y3 FS2 SSC2 Y4Y5 FS3 SSC3 Y6Y7 FS4 SSC4 Y8Y9

0 0 0 Y1_0 FS1_0 SSC1_0 Y2Y3_0 FS2_0 SSC2_0 Y4Y5_0 FS3_0 SSC3_0 Y6Y7_0 FS4_0 SSC4_0 Y8Y9_0

0 0 1 Y1_1 FS1_1 SSC1_1 Y2Y3_1 FS2_1 SSC2_1 Y4Y5_1 FS3_1 SSC3_1 Y6Y7_1 FS4_1 SSC4_1 Y8Y9_1

0 1 0 Y1_2 FS1_2 SSC1_2 Y2Y3_2 FS2_2 SSC2_2 Y4Y5_2 FS3_2 SSC3_2 Y6Y7_2 FS4_2 SSC4_2 Y8Y9_2

0 1 1 Y1_3 FS1_3 SSC1_3 Y2Y3_3 FS2_3 SSC2_3 Y4Y5_3 FS3_3 SSC3_3 Y6Y7_3 FS4_3 SSC4_3 Y8Y9_3

1 0 0 Y1_4 FS1_4 SSC1_4 Y2Y3_4 FS2_4 SSC2_4 Y4Y5_4 FS3_4 SSC3_4 Y6Y7_4 FS4_4 SSC4_4 Y8Y9_4

1 0 1 Y1_5 FS1_5 SSC1_5 Y2Y3_5 FS2_5 SSC2_5 Y4Y5_5 FS3_5 SSC3_5 Y6Y7_5 FS4_5 SSC4_5 Y8Y9_5

1 1 0 Y1_6 FS1_6 SSC1_6 Y2Y3_6 FS2_6 SSC2_6 Y4Y5_6 FS3_6 SSC3_6 Y6Y7_6 FS4_6 SSC4_6 Y8Y9_6

1 1 1 Y1_7 FS1_7 SSC1_7 Y2Y3_7 FS2_7 SSC2_7 Y4Y5_7 FS3_7 SSC3_7 Y6Y7_7 FS4_7 SSC4_7 Y8Y9_7

Addr.

04h 13h 10h-12h 15h 23h 20h-22h 25h 33h 30h-32h 35h 43h 40h-42h 45h

Offset

(1)

(1) Address Offset refers to the byte address in the Configuration Register on following pages.

14 Submit Documentation Feedback Copyright © 2007–2010, Texas Instruments Incorporated

Product Folder Link(s): CDCE949 CDCEL949