User manual

Table Of Contents

- Read This First

- Contents

- Figures

- Tables

- Examples

- Cautions

- Introduction

- Architectural Overview

- Central Processing Unit

- Memory and I/O Spaces

- Program Control

- Addressing Modes

- Assembly Language Instructions

- Instruction Set Summary

- How To Use the Instruction Descriptions

- Instruction Descriptions

- ABS

- ABS

- ADD

- ADD

- ADD

- ADD

- ADDC

- ADDC

- ADDS

- ADDS

- ADDT

- ADDT

- ADRK

- AND

- AND

- AND

- APAC

- APAC

- B

- BACC

- BANZ

- BANZ

- BCND

- BCND

- BIT

- BIT

- BITT

- BITT

- BLDD

- BLDD

- BLDD

- BLDD

- BLDD

- BLPD

- BLPD

- BLPD

- BLPD

- CALA

- CALL

- CC

- CC

- CLRC

- CLRC

- CMPL

- CMPR

- DMOV

- DMOV

- IDLE

- IN

- IN

- INTR

- LACC

- LACC

- LACC

- LACL

- LACL

- LACL

- LACT

- LACT

- LAR

- LAR

- LAR

- LDP

- LDP

- LPH

- LPH

- LST

- LST

- LST

- LST

- LT

- LT

- LTA

- LTA

- LTD

- LTD

- LTD

- LTP

- LTP

- LTS

- LTS

- MAC

- MAC

- MAC

- MAC

- MACD

- MACD

- MACD

- MACD

- MACD

- MAR

- MAR

- MPY

- MPY

- MPY

- MPYA

- MPYA

- MPYS

- MPYS

- MPYU

- MPYU

- NEG

- NEG

- NMI

- NOP

- NORM

- NORM

- NORM

- OR

- OR

- OR

- OUT

- OUT

- PAC

- POP

- POP

- POPD

- POPD

- PSHD

- PSHD

- PUSH

- RET

- RETC

- ROL

- ROR

- RPT

- RPT

- SACH

- SACH

- SACL

- SACL

- SAR

- SAR

- SBRK

- SETC

- SETC

- SFL

- SFR

- SFR

- SPAC

- SPH

- SPH

- SPL

- SPL

- SPLK

- SPLK

- SPM

- SQRA

- SQRA

- SQRS

- SQRS

- SST

- SST

- SUB

- SUB

- SUB

- SUB

- SUBB

- SUBB

- SUBC

- SUBC

- SUBS

- SUBS

- SUBT

- SUBT

- TBLR

- TBLR

- TBLR

- TBLW

- TBLW

- TBLW

- TRAP

- XOR

- XOR

- XOR

- ZALR

- ZALR

- On-Chip Peripherals

- Synchronous Serial Port

- Asynchronous Serial Port

- TMS320C209

- Register Summary

- TMS320C1x/C2x/C2xx/C5x Instruction Set Comparison

- Program Examples

- Submitting ROM Codes to TI

- Design Considerations for Using XDS510 Emulator

- E.1 Designing Your Target System’s Emulator Connector (14-Pin Header)

- E.2 Bus Protocol

- E.3 Emulator Cable Pod

- E.4 Emulator Cable Pod Signal Timing

- E.5 Emulation Timing Calculations

- E.6 Connections Between the Emulator and the Target System

- E.7 Physical Dimensions for the 14-Pin Emulator Connector

- E.8 Emulation Design Considerations

- Glossary

- Index

Boot Loader

4-17

Memory and I/O Spaces

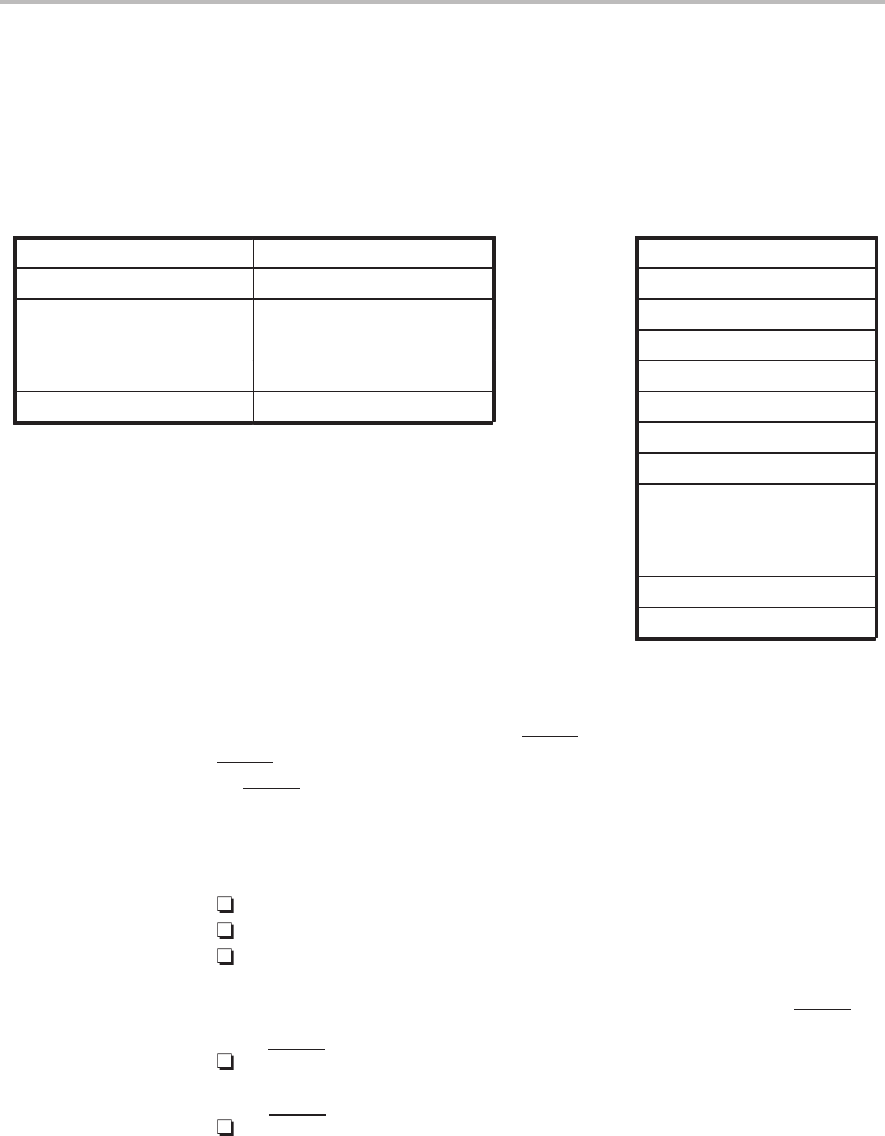

Figure 4–9 shows how to store a 16-bit program into the 8-bit EPROM. A sub-

script h (for example, on Word1

h

) indicates the high-byte and a subscript l (for

example, on Word1

l

) indicates the low byte.

Figure 4–9. Storing the Program in the EPROM

16-Bit Program 8-Bit EPROM

15 8 7 0 Address 7 0

Word1

h

Word1

l

8000h Destination

h

Word2

h

Word2

l

8001h Destination

l

•. • 8002h Length N

h

• • 8003h Length N

l

• • 8004h Word1

h

Wordn

h

Wordn

l

8005h Word1

l

8006h Word2

h

8007h Word2

l

••

••

••

nnnEh Wordn

h

nnnFh Wordn

l

4.5.4 Enabling the Boot Loader

To enable the boot loader, tie the BOOT pin low and reset the device. The

BOOT

pin is sampled only at reset. If you don’t want to use the boot loader,

tie BOOT

high before initiating a reset.

Three main conditions occur at reset that ensure proper operation of the boot

loader:

All maskable interrupts are globally disabled (INTM bit = 1).

On-chip DARAM block B0 is mapped to data space (CNF bit = 0).

Seven wait states are selected for program and data spaces.

After a hardware reset, the processor either executes the boot loader software

or skips execution of the boot loader, depending on the level on the BOOT

pin:

If BOOT is low, the processor branches to the location of the on-chip boot

loader program.

If BOOT is high, the processor begins program execution at the address

pointed to by the reset vector at address 0000h in program memory.