User manual

Table Of Contents

- Read This First

- Contents

- Figures

- Tables

- Examples

- Cautions

- Introduction

- Architectural Overview

- Central Processing Unit

- Memory and I/O Spaces

- Program Control

- Addressing Modes

- Assembly Language Instructions

- Instruction Set Summary

- How To Use the Instruction Descriptions

- Instruction Descriptions

- ABS

- ABS

- ADD

- ADD

- ADD

- ADD

- ADDC

- ADDC

- ADDS

- ADDS

- ADDT

- ADDT

- ADRK

- AND

- AND

- AND

- APAC

- APAC

- B

- BACC

- BANZ

- BANZ

- BCND

- BCND

- BIT

- BIT

- BITT

- BITT

- BLDD

- BLDD

- BLDD

- BLDD

- BLDD

- BLPD

- BLPD

- BLPD

- BLPD

- CALA

- CALL

- CC

- CC

- CLRC

- CLRC

- CMPL

- CMPR

- DMOV

- DMOV

- IDLE

- IN

- IN

- INTR

- LACC

- LACC

- LACC

- LACL

- LACL

- LACL

- LACT

- LACT

- LAR

- LAR

- LAR

- LDP

- LDP

- LPH

- LPH

- LST

- LST

- LST

- LST

- LT

- LT

- LTA

- LTA

- LTD

- LTD

- LTD

- LTP

- LTP

- LTS

- LTS

- MAC

- MAC

- MAC

- MAC

- MACD

- MACD

- MACD

- MACD

- MACD

- MAR

- MAR

- MPY

- MPY

- MPY

- MPYA

- MPYA

- MPYS

- MPYS

- MPYU

- MPYU

- NEG

- NEG

- NMI

- NOP

- NORM

- NORM

- NORM

- OR

- OR

- OR

- OUT

- OUT

- PAC

- POP

- POP

- POPD

- POPD

- PSHD

- PSHD

- PUSH

- RET

- RETC

- ROL

- ROR

- RPT

- RPT

- SACH

- SACH

- SACL

- SACL

- SAR

- SAR

- SBRK

- SETC

- SETC

- SFL

- SFR

- SFR

- SPAC

- SPH

- SPH

- SPL

- SPL

- SPLK

- SPLK

- SPM

- SQRA

- SQRA

- SQRS

- SQRS

- SST

- SST

- SUB

- SUB

- SUB

- SUB

- SUBB

- SUBB

- SUBC

- SUBC

- SUBS

- SUBS

- SUBT

- SUBT

- TBLR

- TBLR

- TBLR

- TBLW

- TBLW

- TBLW

- TRAP

- XOR

- XOR

- XOR

- ZALR

- ZALR

- On-Chip Peripherals

- Synchronous Serial Port

- Asynchronous Serial Port

- TMS320C209

- Register Summary

- TMS320C1x/C2x/C2xx/C5x Instruction Set Comparison

- Program Examples

- Submitting ROM Codes to TI

- Design Considerations for Using XDS510 Emulator

- E.1 Designing Your Target System’s Emulator Connector (14-Pin Header)

- E.2 Bus Protocol

- E.3 Emulator Cable Pod

- E.4 Emulator Cable Pod Signal Timing

- E.5 Emulation Timing Calculations

- E.6 Connections Between the Emulator and the Target System

- E.7 Physical Dimensions for the 14-Pin Emulator Connector

- E.8 Emulation Design Considerations

- Glossary

- Index

Interrupts

5-29

Program Control

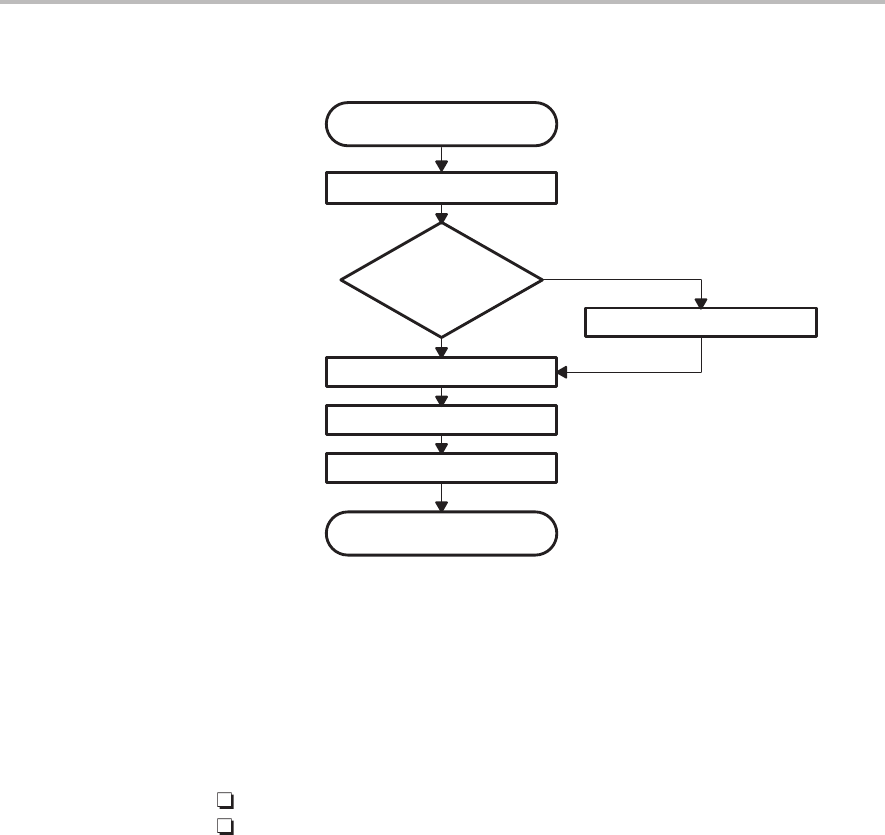

Figure 5–10. Nonmaskable Interrupt Operation Flow Chart

Interrupt request sent to CPU

Interrupt acknowledged

TRAP

instruction?

Yes

No

INTM bit set to 1

PC saved on stack

Interrupt service routine run

Return instruction restores PC

Program continues

5.6.8 Interrupt Service Routines (ISRs)

After an interrupt has been requested and acknowledged, the CPU follows an

interrupt vector to the ISR. The ISR is the program code that actually performs

the tasks requested by the interrupt. While performing these tasks, the ISR

may also be:

Saving and restoring register values

Managing ISRs within ISRs

Saving and restoring register values

Only the incremented program counter value is stored automatically before

the CPU enters an interrupt service routine (ISR). You must design the ISR to

save and then restore any other important register values. For example, if your

ISR will need to perform a multiplication, it will need to use the product register

(PREG). If the value currently in the PREG must be in the PREG after the ISR,

the ISR must save the value, perform the new multiplication, store the resulting

PREG value, and then reload the original value. You may find that certain reg-

isters will need to be saved during most ISRs. If so, you can copy a common

save and restore routine and then individualize it for each interrupt.