User`s manual

Chapter 2: Installation

2-25

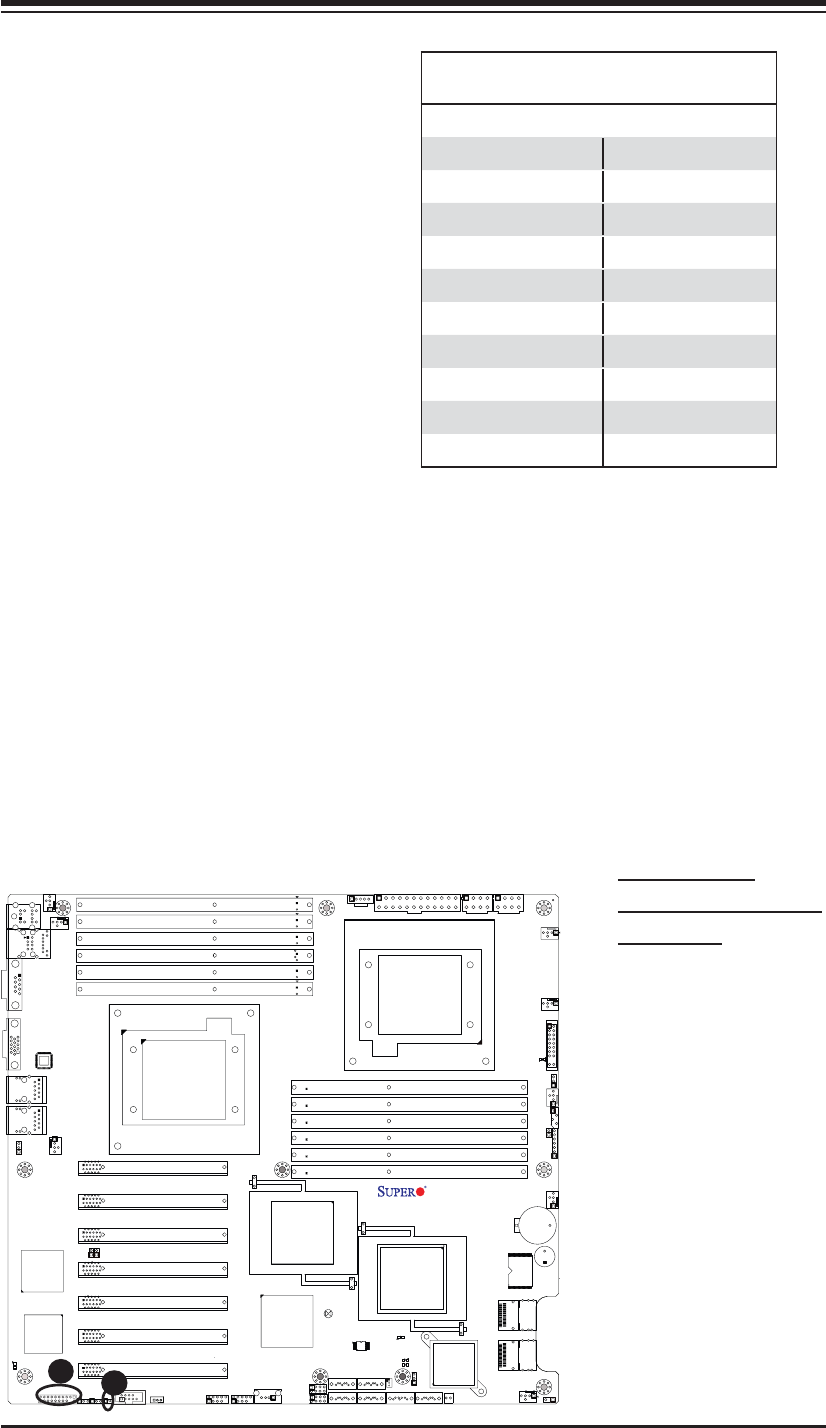

Trusted Platform Module Header

A Trusted Platform Module (TPM)

header is located on the motherboard

to provide TPM support to enhance

data integrity and system security.

Refer to the table on the right for pin

defi nitions.

Trusted Platform Module (TPM) Header

Pin Defi nitions

Pin# Defi nition Pin # Defi nition

1 LPC Clock 2 GND

3 LPC FRAME# 4 Key

5 LPC Reset# 6 +5V (X)

7 LAD3 8 LAD2

9 +3.3V 10 LAD1

11 LAD0 12 GND

13 SCL 14 SDAT

15 +3V_DUAL 16 SERIRQ (X)

17 GND 18 CLKRUN(X)

19 LPCPD# (X) 20 LDRQ#(X)

Notes:

(X)=TPM does not use the signals.

SCL, SDAT are I

2

C bus clock and data.

SPI BIOS

I-SATA1

I-SATA0

I-SATA5

I-SATA4

JBT1

SATA-SGPIO0

DP5

LED5

DP4

JPL1

JPG1

JPB

JPS1

JWD

JI2C2

JI2C1

JOH1

JD1

LAN1

VGA

FAN5

KB/MS

P2-DIMM3A

FAN6

P2-DIMM3B

JPI2C

JPW1

JPW2

FAN1

P2-DIMM2A

P2-DIMM2B

P2-DIMM1A

P2-DIMM1B

FAN7

COM1

CPU1

JF1

CPU2

IPMI_LAN

USB0/1

PWR_LED

P1-DIMM1B

P1-DIMM1A

FAN2

P1-DIMM2A

SMBus1

LAN2

FAN8

P1-DIMM3B

Slot7 PCI-E 2.0 X8

P1-DIMM3A

FAN3

Slot6 PCI-E 2.0 X8

Slot5 PCI-E 2.0 X8

Battery

Slot4 PCI-E 2.0 X8

Buzzer

Slot3 PCI-E 2.0 X8

FLASH

(IOH36D-1)

BMC

Slot2 PCI-E 2.0 X8

SAS Activity

SAS0~3

ICH10R

SAS4~7

Slot1 PCI-E 2.0 X8

USB4/5

USB3

USB6/7

LSI

SAS2008

FAN4

JPW3

P1-DIMM2B

LAN CTRL

SAS

PHY

I-SATA2

I-SATA3

X8DTH

Rev. 2.0

SATA-SGPIO1

DP6

DP7

Intel

(South Bridge)

5520

Intel

(IOH36D-2)

5520

Intel

RAID Key

JL1

1

1

1

COM2

TPM

JHB1

JWOL1

Wake-On-LAN

JWF1

A

A. TPM Header

B. FP IPMI Heartbeat

LED Header

FP IPMI Heartbeat LED Header

(X8DTH-6F/iF Only)

The Front Panel IPMI Heartbeat LED

connection header (JHB1) is located

next to COM2 port. Connect a cable

here to indicate the status of IPMI

connection. See the layout for the

location of JHB1.

B