Datasheet

STM32F051x Pinouts and pin description

Doc ID 022265 Rev 3 33/105

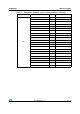

Table 14. Alternate functions selected through GPIOA_AFR registers for port A

Pin name AF0 AF1 AF2 AF3 AF4 AF5 AF6 AF7

PA0 USART2_CTS

TIM2_CH1_

ETR

TSC_G1_IO1 COMP1_OUT

PA1 EVENTOUT USART2_RTS TIM2_CH2 TSC_G1_IO2

PA2 TIM15_CH1 USART2_TX TIM2_CH3 TSC_G1_IO3 COMP2_OUT

PA3 TIM15_CH2 USART2_RX TIM2_CH4 TSC_G1_IO4

PA 4

SPI1_NSS/

I2S1_WS

USART2_CK TSC_G2_IO1 TIM14_CH1

PA 5

SPI1_SCK/

I2S1_CK

CEC

TIM2_CH1_

ETR

TSC_G2_IO2

PA 6

SPI1_MISO/

I2S1_MCK

TIM3_CH1 TIM1_BKIN TSC_G2_IO3 TIM16_CH1 EVENTOUT COMP1_OUT

PA 7

SPI1_MOSI/

I2S1_SD

TIM3_CH2 TIM1_CH1N TSC_G2_IO4 TIM14_CH1 TIM17_CH1 EVENTOUT COMP2_OUT

PA8 MCO USART1_CK TIM1_CH1 EVENTOUT

PA9 TIM15_BKIN USART1_TX TIM1_CH2 TSC_G4_IO1

PA10 TIM17_BKIN USART1_RX TIM1_CH3 TSC_G4_IO2

PA11 EVENTOUT USART1_CTS TIM1_CH4 TSC_G4_IO3 COMP1_OUT

PA12 EVENTOUT USART1_RTS TIM1_ETR TSC_G4_IO4 COMP2_OUT

PA 13 S WDAT I R_O UT

PA14 SWCLK USART2_TX

PA 15

SPI1_NSS/

I2S1_WS

USART2_RX

TIM2_CH1_

ETR

EVENTOUT