User Manual

VEML6030

www.vishay.com

Vishay Semiconductors

Rev. 1.3, 12-May-17

4

Document Number: 84366

For technical questions, contact: sensorstechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

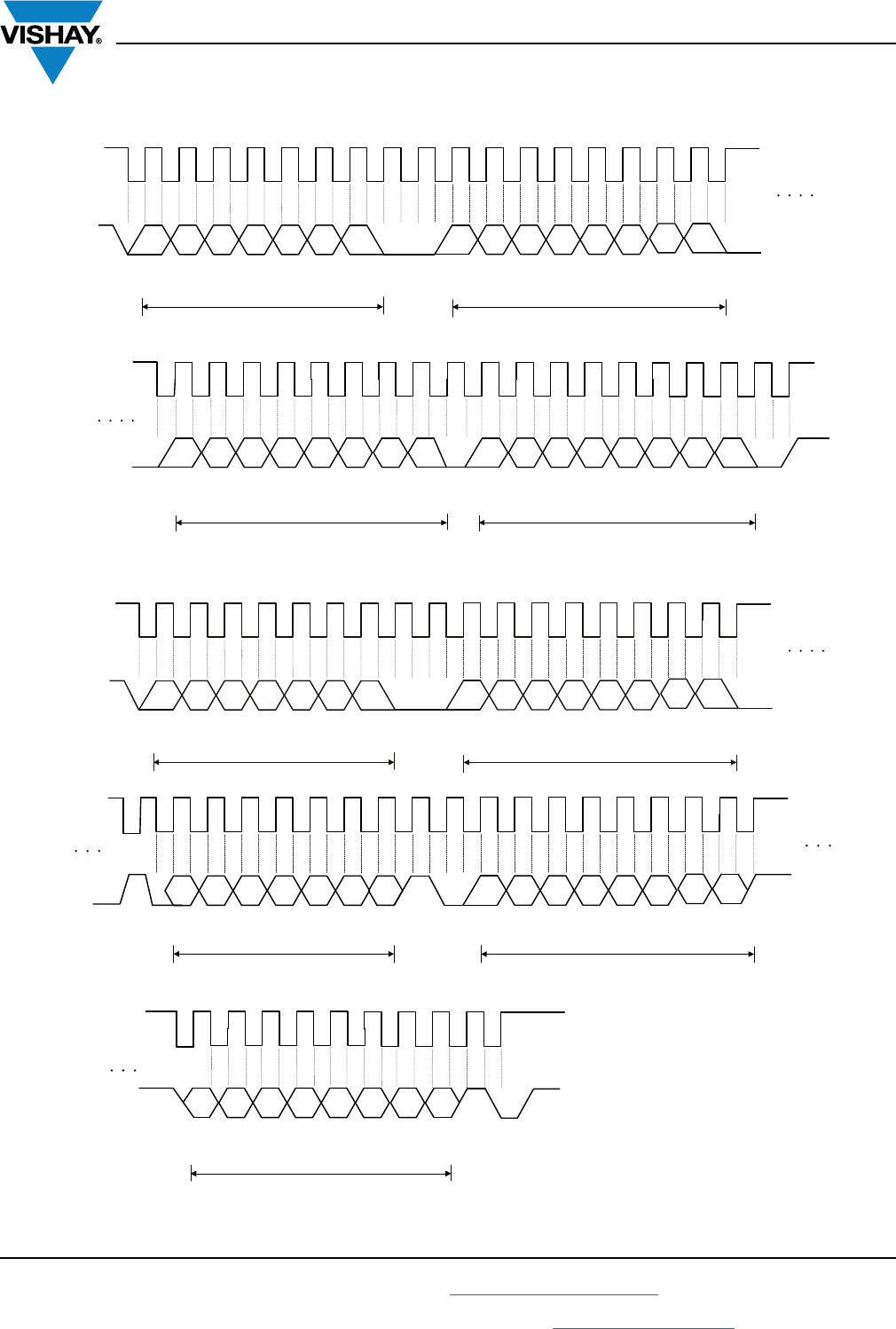

PARAMETER TIMING INFORMATION

Fig. 3 - I

2

C Bus Timing for Sending Word Command Format

Fig. 4 - I

2

C Bus Timing for Receive Word Command Format

ACK ACK

ACKACK

I

2

C bus

clock

(SCLK)

I

2

C bus

data

(SDAT)

I

2

C bus

clock

(SCLK)

I

2

C bus

data

(SDAT)

I

2

C bus slave address byte Command code

Start by

master

Stop by

master

Data byte low Data byte high

SA7 SA1SA2SA3SA4SA5SA6 SA7 SA1SA2SA3SA4SA5SA6 SA0

SA7 SA1SA2SA3SA4SA5SA6 SA0

SA7

SA1SA2SA3SA4SA5SA6

SA0

W

ACK

ACK ACK

I

2

C bus

clock

(SCLK)

I

2

C bus

data

(SDAT)

I

2

C bus slave address byte Command code

Start by

master

SA7 SA1SA2SA3SA4SA5SA6 SA7 SA1SA2SA3SA4SA5SA6

SA0

W

I

2

C bus

clock

(SCLK)

I

2

C bus

data

(SDAT)

Data byte low

Data byte high

ACK by

master

Start by

master

I

2

C bus slave address byte

I

2

C bus

clock

(SCLK)

I

2

C bus

data

(SDAT)

NACK by

master

Stop by

master

SA7 SA1SA2SA3SA4SA5SA6

SA7 SA1SA2SA3SA4SA5SA6 SA0

R

SA7 SA1SA2SA3SA4SA5SA6 SA0