User Manual

VEML6030

www.vishay.com

Vishay Semiconductors

Rev. 1.3, 12-May-17

3

Document Number: 84366

For technical questions, contact: sensorstechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

Note

(1)

Data based on standard I

2

C protocol requirement, not tested in production

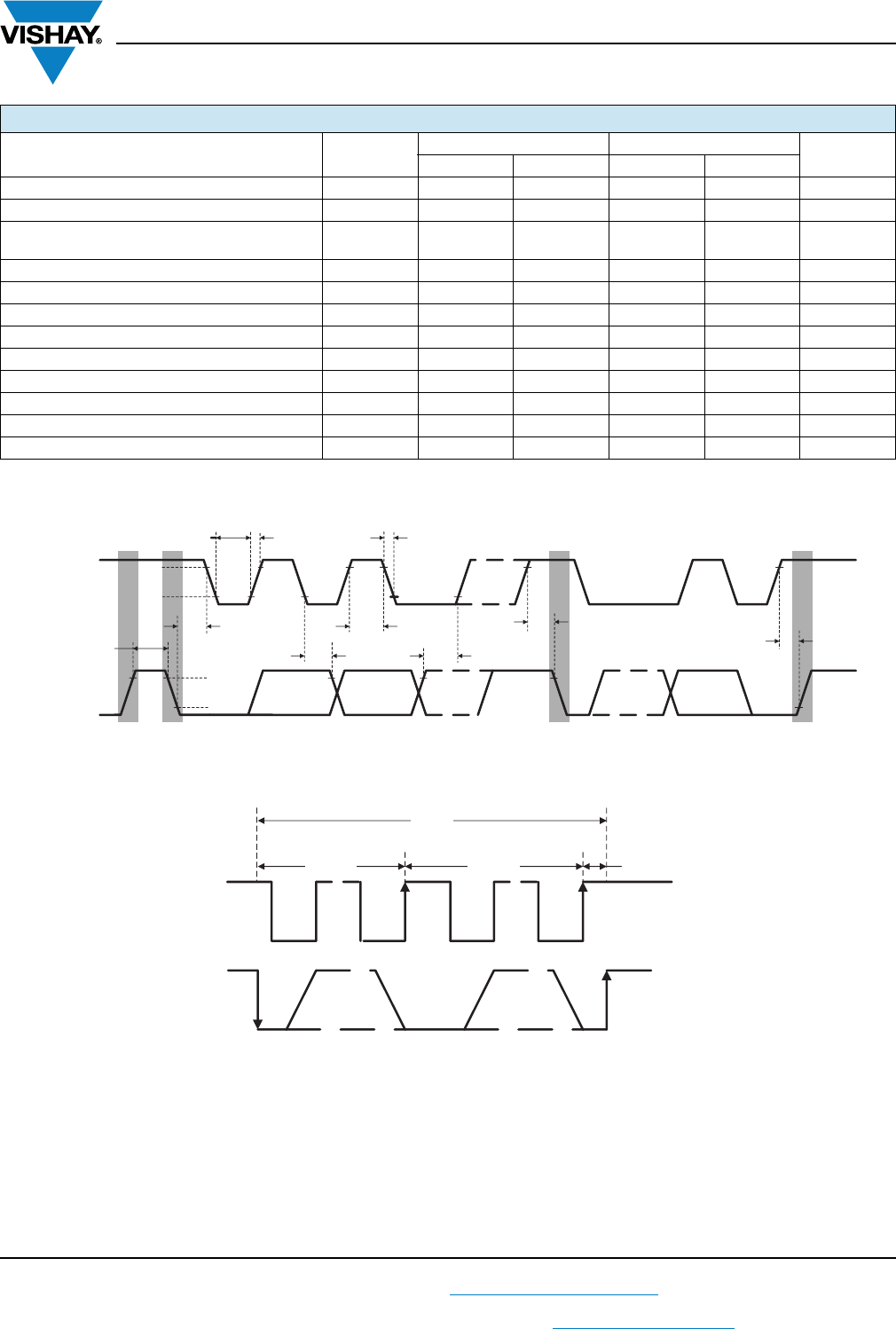

Fig. 2 - I

2

C Timing Diagram

I

2

C TIMING CHARACTERISTICS (T

amb

= 25 °C, unless otherwise specified)

PARAMETER SYMBOL

STANDARD MODE

(1)

FAST MODE

(1)

UNIT

MIN. MAX. MIN. MAX.

Clock frequency f

(SMBCLK)

10 100 10 400 kHz

Bus free time between start and stop condition t

(BUF)

4.7 - 1.3 - μs

Hold time after (repeated) start condition;

after this period, the first clock is generated

t

(HDSTA)

4.0 - 0.6 - μs

Repeated start condition setup time t

(SUSTA)

4.7 - 0.6 - μs

Stop condition setup time t

(SUSTO)

4.0 - 0.6 - μs

Data hold time t

(HDDAT)

0 3450 0 900 ns

Data setup time t

(SUDAT)

250 - 100 - ns

I

2

C clock (SCK) low period t

(LOW)

4.7 - 1.3 - μs

I

2

C clock (SCK) high period t

(HIGH)

4.0 - 0.6 - μs

Detect clock / data low timeout t

(TIMEOUT)

25 35 - - ms

Clock / data fall time t

(F)

- 300 - 300 ns

Clock / data rise time t

(R)

- 1000 - 300 ns

V

IH

V

IL

t

(BUF)

{

{

P

Stop condition

S

Start condition

{

{

PS

Start Stop

I

2

C bus

clock

(SLCK)

I

2

C bus

data

(SDAT)

I

2

C bus

clock

(SLCK)

I

2

C bus

data

(SDAT)

t

(LOW)

t

(R)

t

(F)

V

IH

V

IL

t

(HDSTA)

t

(HDDAT)

t

(HIGH)

t

(SUDAT)

t

(SUSTA)

t

(SUSTO)

t

(LOSEXT)

t

(LOWMEXT)

t

(LOWMEXT)

t

(LOWMEXT)

SCLK

ACK

SDA

ACK