Data Sheet

PRELIMINARY

VS1063a Datasheet

7 SPI BUSES

7.4.3 SDI in VS1001 Compatibility Mode (deprecated)

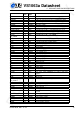

BSYNC

SDATA

DCLK

D7 D6 D5 D4 D3 D2 D1 D0

Figure 4: BSYNC signal - one byte transfer

When VS1063a is running in VS1001 compatibility mode, a BSYNC signal must be generated

to ensure correct bit-alignment of the input bitstream. The first DCLK sampling edge (rising or

falling, depending on selected polarity), during which the BSYNC is high, marks the first bit of

a byte (LSB, if LSB-first order is used, MSB, if MSB-first order is used). If BSYNC is ’1’ when

the last bit is received, the receiver stays active and next 8 bits are also received.

BSYNC

SDATA

DCLK

D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0

Figure 5: BSYNC signal - two byte transfer

7.4.4 Passive SDI Mode

If SM_NEWMODE is 0 and SM_SDISHARE is 1, the operation is otherwise like the VS1001

compatibility mode, but bits are only received while the BSYNC signal is ’1’. Rising edge of

BSYNC is still used for synchronization.

Version: 0.42, 2011-11-24 20