User Manual

Apollo3 Blue Datasheet

DS-A3-0p9p1 Page 791 of 909 2019 Ambiq Micro, Inc.

All rights reserved.

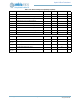

21.14Serial Peripheral Interface (SPI) Slave Interface

Table 1157: Serial Peripheral Interface (SPI) Slave Interface

Symbol Parameter Min Typ Max Unit

F

SCLK

SCLK frequency range - - 8 MHz

B

FIFO

FIFO size 128 Bytes

T

SCLK_LO

Clock low time

1/2F

S-

CLK(max)

-- s

T

SCLK_HI

Clock high time

1/2F

S-

CLK(max)

-- s

T

CE_LEAD

Chip enable low to first SCLK edge - - - ns

T

CE_LAG

Chip enable high to last SCLK edge - - - ns

T

CE_SDO

Chip enable low to MISO data output - - - ns

T

CE_SDZ

Chip enable high to MISO data tri-state - - - ns

T

SU_SI

MOSI input data setup time - - - ns

T

HD_SI

MOSI input data hold time - - - ns

T

HD_SO

MISO output data hold time - - - ns

T

VALID,SO

MISO output data valid time - - - ns

SCLK

MOSI

T

HD_SI

T

SCLK_LO

T

SCLK_HI

T

SCLK_LO

T

SCLK_HI

1/F

SCLK

T

HD_SO

T

VALID_SO

T

SU_MI

SPOL = 0

SPOL = 1

MISO

T

SU_SI

T

SCLK_R

T

SCLK_F

CE

T

CE_SDO

T

CE_LEAD

T

CE_LAG

T

CE_SDZ