User Manual

Apollo3 Blue Datasheet

DS-A3-0p9p1 Page 661 of 909 2019 Ambiq Micro, Inc.

All rights reserved.

13.21.2.63INTEN Register

Counter/Timer Interrupts: Enable

OFFSET: 0x00000200

INSTANCE 0 ADDRESS: 0x40008200

Set bits in this register to allow this module to generate the corresponding interrupt.

3CFGB1 0x0RW

CTIMER B1 input configuration

CT7 = 0x1 - Input is CT7

CT6 = 0x0 - Input is CT6

2CFGA1 0x0RW

CTIMER A1 input configuration

CT5 = 0x1 - Input is CT5

CT4 = 0x0 - Input is CT4

1CFGB0 0x0RW

CTIMER B0 input configuration

CT3 = 0x1 - Input is CT3

CT2 = 0x0 - Input is CT2

0CFGA0 0x0RW

CTIMER A0 input configuration

CT1 = 0x1 - Input is CT1

CT0 = 0x0 - Input is CT0

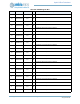

Table 945: INTEN Register

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0

0

9

0

8

0

7

0

6

0

5

0

4

0

3

0

2

0

1

0

0

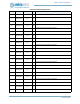

CTMRB7C1INT

CTMRA7C1INT

CTMRB6C1INT

CTMRA6C1INT

CTMRB5C1INT

CTMRA5C1INT

CTMRB4C1INT

CTMRA4C1INT

CTMRB3C1INT

CTMRA3C1INT

CTMRB2C1INT

CTMRA2C1INT

CTMRB1C1INT

CTMRA1C1INT

CTMRB0C1INT

CTMRA0C1INT

CTMRB7C0INT

CTMRA7C0INT

CTMRB6C0INT

CTMRA6C0INT

CTMRB5C0INT

CTMRA5C0INT

CTMRB4C0INT

CTMRA4C0INT

CTMRB3C0INT

CTMRA3C0INT

CTMRB2C0INT

CTMRA2C0INT

CTMRB1C0INT

CTMRA1C0INT

CTMRB0C0INT

CTMRA0C0INT

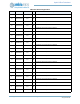

Table 946: INTEN Register Bits

Bit Name Reset RW Description

31 CTMRB7C1INT 0x0 RW

Counter/Timer B7 interrupt based on COMPR1.

30 CTMRA7C1INT 0x0 RW

Counter/Timer A7 interrupt based on COMPR1.

29 CTMRB6C1INT 0x0 RW

Counter/Timer B6 interrupt based on COMPR1.

28 CTMRA6C1INT 0x0 RW

Counter/Timer A6 interrupt based on COMPR1.

Table 944: INCFG Register Bits

Bit Name Reset RW Description