Specifications

Table Of Contents

Ra-01 规格书 V1.0

Copyright © 2019 Shenzhen Ai-Thinker Technology Co., Ltd All Rights Reserved

第 10 页 共 15 页

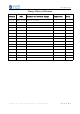

No. Name

Function instruction

1 ANT Antenna

2 GND Ground

3 3.3V 3.3V power supply(VDD)

4 RESET Reset

5 DIO0 Digital IO0 software configuration

6 DIO1 Digital IO1 software configuration

7 DIO2 Digital IO2 software configuration

8 DIO3 Digital IO3 software configuration

9 GND ground

10 DIO4 Digital IO4 software configuration

11 DIO5 Digital IO5 software configuration

12 SCK SPI clock input

13 MISO SPI data output

14 MOSI SPI data input

15 NSS SPI Selection input

16 GND ground

The six general IO pin of SX1278 can be available in LoRa™ mode.

Their mapping depends on the configuration of the two registers RegDioMapping1 and RegDioMapping2.

Operating

Mode

DIOx

Mapping

DIO5 DIO4 DIO3 DIO2 DIO1 DIO0

All

00 ModeReady

CadDetec

ted

CadDone

Fhss

Change

Channel

RxRimeout RxDone

01 ClkOut PllLock

Valid

Header

Fhss

Change

Channel

Fhss

Change

Channel

TxDone

10 ClkOut PllLock

PayloadCrc

Error

Fhss

Change

Channel

CadDetected CadDoe

11 - - - - - -