User's Manual

Smart Machine Smart Decision

SIM5320A_Hardware Design_V1.01 2011-2-29

48

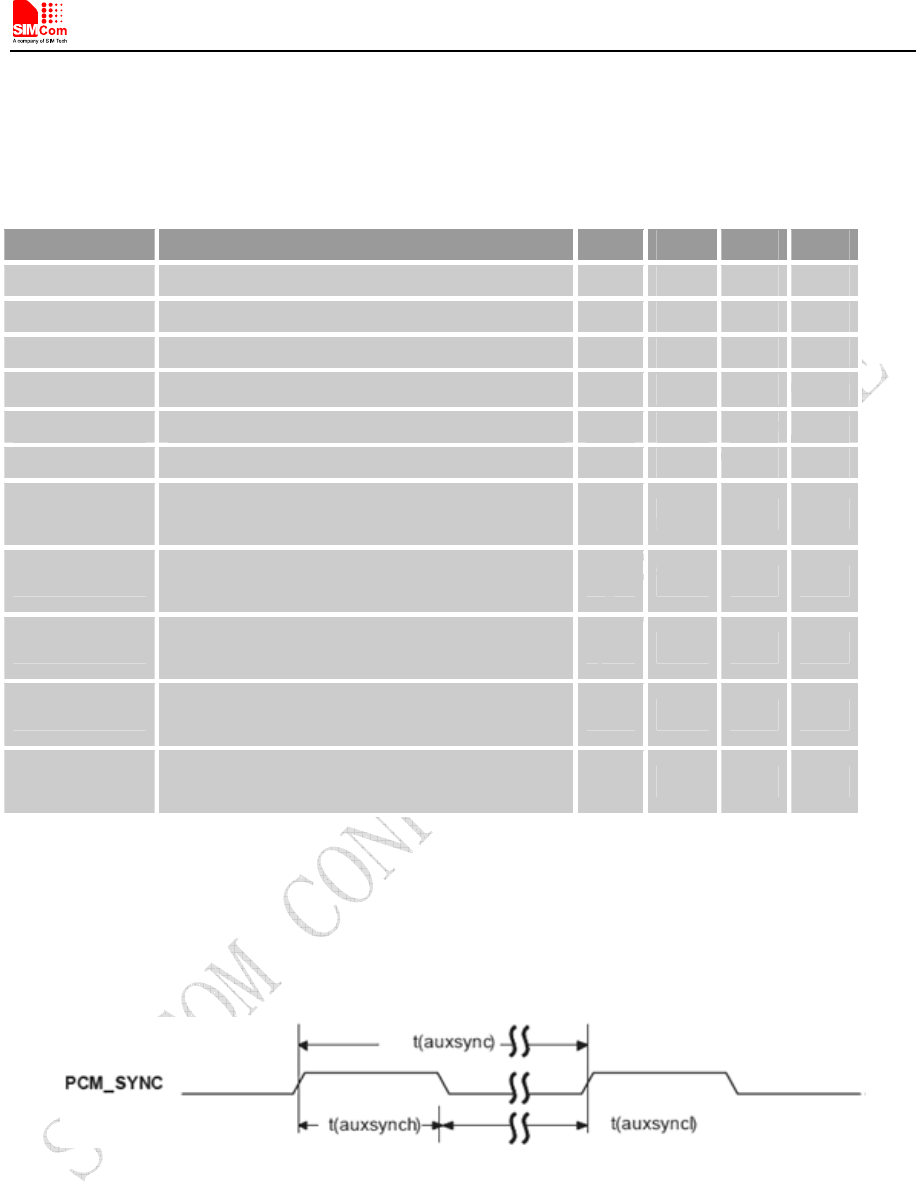

Figure 35: MODULE to EXT CODEC timing

Table 30: Timing parameters

Parameter Description Min Typ Max Unit

T(auxsync) AUX_PCM_SYNC cycle time – 125 - μs

T(auxsynch) AUX_PCM_SYNC high time 62.4 62.5 - μs

T(auxsyncl) AUX_PCM_SYNC low time 62.4 62.5 - μs

T(auxclk)* AUX_PCM_CLK cycle time - 7.8 – μs

T(auxclkh) AUX_PCM_CLK high time 3.8 3.9 – μs

T(auxclkl) AUX_PCM_CLK low time 3.8 3.9 – μs

T(suauxsync)

AUX_PCM_SYNC setup time high before

falling edge of PCM_CLK

1.95 – – μs

T(hauxsync)

AUX_PCM SYNC hold time after falling edge

of PCM_CLK

1.95 – – μs

T(suauxdin)

AUX_PCM_DIN setup time before falling

edge of AUX_PCM_CLK

70 – – ns

T(hauxdin)

AUX_PCM_DIN hold time after falling edge

of AUX_PCM_CLK

20 – – ns

T(pauxdout)

Delay from AUX_PCM_CLK rising to

AUX_PCM_DOUT valid

– – 50 ns

*Note: T(auxclk) = 1/(128 KHz).

Primary PCM (2048 KHz PCM clock)

SIM5320A also supports 2.048 MHz PCM data and sync timing for

υ-law codec. This is called the

primary PCM interface. User can use AT command to take the mode you want as discussed above.

Figure36:Synchronytiming