User Manual

FlexPak 3000 Drives: Original Register Map

5-9

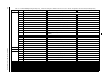

23 ANLG MAN REF ZERO ADJ (P.105) Offset removed from the analog manual reference signal

24

TRIM REF REGISTER (P.107) Trim reference value % TOP SPEED (P.011) * 10

25

TRIM REFERENCE SELECT (P.108) Trim reference selection 0=REGISTER; 1=ANALOG MANUAL;

2=

ANALOG IN 1; 3=NETW IN REG 1;

4=

NETW IN REG 2; 5=NETW IN REG 3;

6=

ANALOG IN 2

26

TRIM MODE SELECT (P.110) Type of trim mode selected 0=NO TRIM; 1=INCREMENTAL;

2=

PROPORTIONAL

27

AUTO MODE MIN BYPASS (P.111) Disables minimum speed limit while in auto mode 0=OFF; 1=ON (min speed bypassed)

28

AUTO MODE RAMP BYPASS (P.112) Bypasses speed loop S-curve block while drive is in auto 0=OFF; 1=ON (rate limit bypassed)

29

STOP SPEED THRESHOLD (P.113) Speed threshold at which the main contactor will open

during a controlled stop

RPM

30

STOP MODE SELECT (P.114) Selects how drive responds to a normal stop command 0=RAMP; 1=COAST/DB; 2=CURRENT LIMIT

31 TRIM OUTPUT (P.197)

Signal that trims the selected speed/voltage loop reference

4095 at TOP SPEED (P.011)

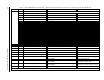

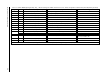

Table 5.9 – FlexPak 3000 Original Register Map, Drop_2: Master Write Registers, FULL Connection. Tunable Data (Drive Input Data)

Register Bit Parameter Name (Number) Description Settings

32 Reserved

33

NORMALIZED INERTIA (P.222) Combined inertia of motor and load seconds*100

34

OCL REF REGISTER (P.801) Outer control loop reference 4095

35

OCL REF RAMP TIME (P.802) Ramp time for OCL reference seconds * 10

36

OCL REF ROUNDING (P.803) Amount of smoothing of the outer control loop reference %

37

OCL LEADLAG SELECT (P.805) Outer control loop lead/lag block select 0=LEAD/LAG; 1=BYPASS; 2 = LAG/LEAD

38

OCL LEADLAG LOW FREQ (P.806) OCL lead/lag block low break frequency radians/second * 100

39

OCL LEADLAG RATIO (P.807) Ratio between low and high frequencies of OCL

40 JOG ACCEL/DECEL TIME (P.013) Minimum time in which jog reference can change from

zero to

TOP SPEED (P.011) and from TOP SPEED to zero

seconds * 10

41

ANLG AUTO GAIN ADJ (P.101) Scales analog auto reference signal gain * 1000

42

ANLG AUTO ZERO ADJ (P.102) Offset removed from analog auto reference signal

Tunable data are updated by the regulator approximately every 600 msec when Tune/Config Input Enable bit = 1.

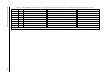

Table 5.8 – FlexPak 3000 Original Register Map, Drop_2: Master Read Registers, FULL Connection. Tunable, Configurable, and Status Data (Drive Output Data) (Continued)

Register Bit Parameter Name (Number) Description Settings

Tunable, configurable, and status data are updated by the regulator approximately every 600 msec.