Owner manual

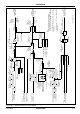

APPENDIX D

FlexPak 3000 49’1340 e

D-6

From Speed Reference

Mode Select Block Diagram

(SPD LOOP REFERENCE)

SPD LOOP LAG FREQ

SPD LOOP PI PROP GAIN

(SPD LOOP OUTPUT)

SPD LOOP

LAG BYPASS

Off

(SPD LOOP ERROR)

WLG

LAG

(SPD LOOP

LAG OUTPUT)

PI

KP

HI

WLD

LO

POSITIVE CURRENT LIM

POS CURRENT

LIM SEL

*REGISTER

ANALOG IN 1

ANALOG IN 2

NETW IN REG 1, 2, 3

From Network

From I/O Expansion

Inputs Block Diagram

{

(SPD LOOP FEEDBACK)

To CML Reference

Block Diagram

To CML Reference

Block Diagram

*ARMATURE VOLT

DC TACH

AC TACH

PULSE TACH

FEEDBACK

SELECT

(ANALOG TACH FEEDBACK)

(PULSE TACH

FEEDBACK)

SPD LEADLAG LOW FREQ

SPD LEADLAG RATIO

* = Default Selection

LEAD/LAG

or

LAG/LEAD

WLD

WRATIO

MOTOR RATED

ARM VOLTS

ARM VOLTAGE

GAIN ADJ

ARM VOLTAGE

ZERO ADJ

(ARMATURE VOLTAGE)

SOFTWARE SCALING

A/D

Armature

Voltage

(internal)

(CML FEEDBACK)

8 sample average

SOFTWARE

SCALING

IR COMPENSATION

(IR COMPENSATION TP)

ANALOG TACH

ZERO ADJ

ANALOG TACH

GAIN ADJ

ANLG TACH

VOLTS/1000

SOFTWARE SCALING

Analog Tachometer

(+ hi) terminal 21

(+ lo) terminal 22

(COM) terminal 23

Pulse Tachometer

(from optional

pulse tach kit)

+

-

A/D

TOP SPEED

SOFTWARE SCALING

F/D

PULSE TACH PPR PULSE TACH QUADRATURE

+

D.5(E)

P.295

P.297

P.215

P.217

P.298

P.005

D.13

P.299

D.9(A)

D.9(B)

P.223

P.211

P.009

P.204

P.205

P.201

P.206

P.203

P.011

P.207

P.208

P.292

P.291

P.202

P.290

P.289

P.200

P.214

P.213

*ZERO

SPD LOOP PI INIT VAL

ANALOG MANUAL TRIM REF

SPD LOOP PI INIT SEL

1)

Netw. Drop 2, Reg. 32

To CML Reference

Block Diagram

SPD LOOP

PI LEAD FREQ

NEGATIVE

CURRENT LIM

ANALOG IN 2

NETW IN REG 1, 2, 3

From Network

From I/O Expansion

Inputs Block Diagram

{

NEG CURRENT

LIM SEL

*REGISTER

ANALOG IN 1

EN

P.212

D.13

P.006

D.9(C)

P.224

(A)

(B)

(B)

(A)

Network Drop 1, Reg. 39

D.4 ANALOG MAN TRIM REF

P.194

A

B

A * B

1000

UNDERWIND ENABLE 1)

Netw. Drop 1, Reg. 32, Bit 5

SPEED FEEDBACK GAIN 1)

Netw. Drop 1, Reg. 38

P.296

D.14(D)

To Level Detectors

.

Netw.Drop 1, Reg. 32, Bit 6

INIT

0

RST

OR

Internal Sequenzing

(drive stopped)

* BYPASS

LEAD/LAG

LAG/LEAD

SPD LEADLAG

SELECT

P.216

* BYPASS

ENABLE

OFF

*ON

(Other)

NETWORK

P.000 CSS

SPD LOOP PI RESET

Feedback Multiplier

Bypass 2)

EN

NOTE 1) Network only register. CSS must be set to NETWORK

and NETW REGISTER MAP SEL = ALTERNATE

NOTE 2) User inaccessible select, the multiplier block is BYPASS'ed

unless the conditions of NOTE 1 are met.

NOTE 3) Also enables/disables on inverter CML ref. block diagram.

NEG CURRENT LIM INV EN 3)

P.226

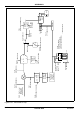

Figure D.6 - Speed Loop