User manual

Calculating Program Timing

Chapter 9

9-8

Bit and Word Instructions for PLC5/10, 5/12, 5/15, and 5/25

Processors

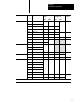

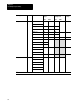

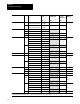

Table 9.N shows timing and memory requirements for bit and word

instructions for PLC-5/10, -5/12, -5/15, and -5/25 processors.

Table 9.N

Timing

and Memory Requirements for Bit and W

ord Instructions

for PLC5/10, 5/12, 5/15, and 5/25 Processors

Category Code Title

Execution Time (µs)

Integer

True False

Execution Time (µs)

Floating Point

True False

Words of

Memory

2

Relay XIC examine if closed

1.3 0.8 1

1

XIO examine if open

OTL output latch

1.6

OTU output unlatch

OTE output energize 1.6 1.6

Branch branch end

0.8 0.8 1

next branch

branch start

Timer and Counter TON timer on (0.01 base)

(1.0 base)

39

44

27

28

23

TOF timer off (0.01 base)

(1.0 base)

30

30

43

51

RTO retentive timer on

(0.01 base)

(1.0 base)

39

44

24

24

CTU count up 32

34

CTD count down 34

RES reset 30 14

1

For

every bit address above the first 256 words of memory in the data table, add 0.8

µ

s to the execution time and 1 wordd of memory to the requirements.

2

Use

the smaller number if all addresses are below word 4096; use the larger number if all addresses are above 4096.