Datasheet

Table Of Contents

- 1. Overview

- 2. Central Processing Unit (CPU)

- 3. Memory

- 4. Special Function Registers (SFRs)

- 5. Electrical Characteristics

- Package Dimensions

R8C/18 Group, R8C/19 Group 4. Special Function Registers (SFRs)

Rev.1.40 Apr 14, 2006 Page 20 of 38

REJ03B0124-0140

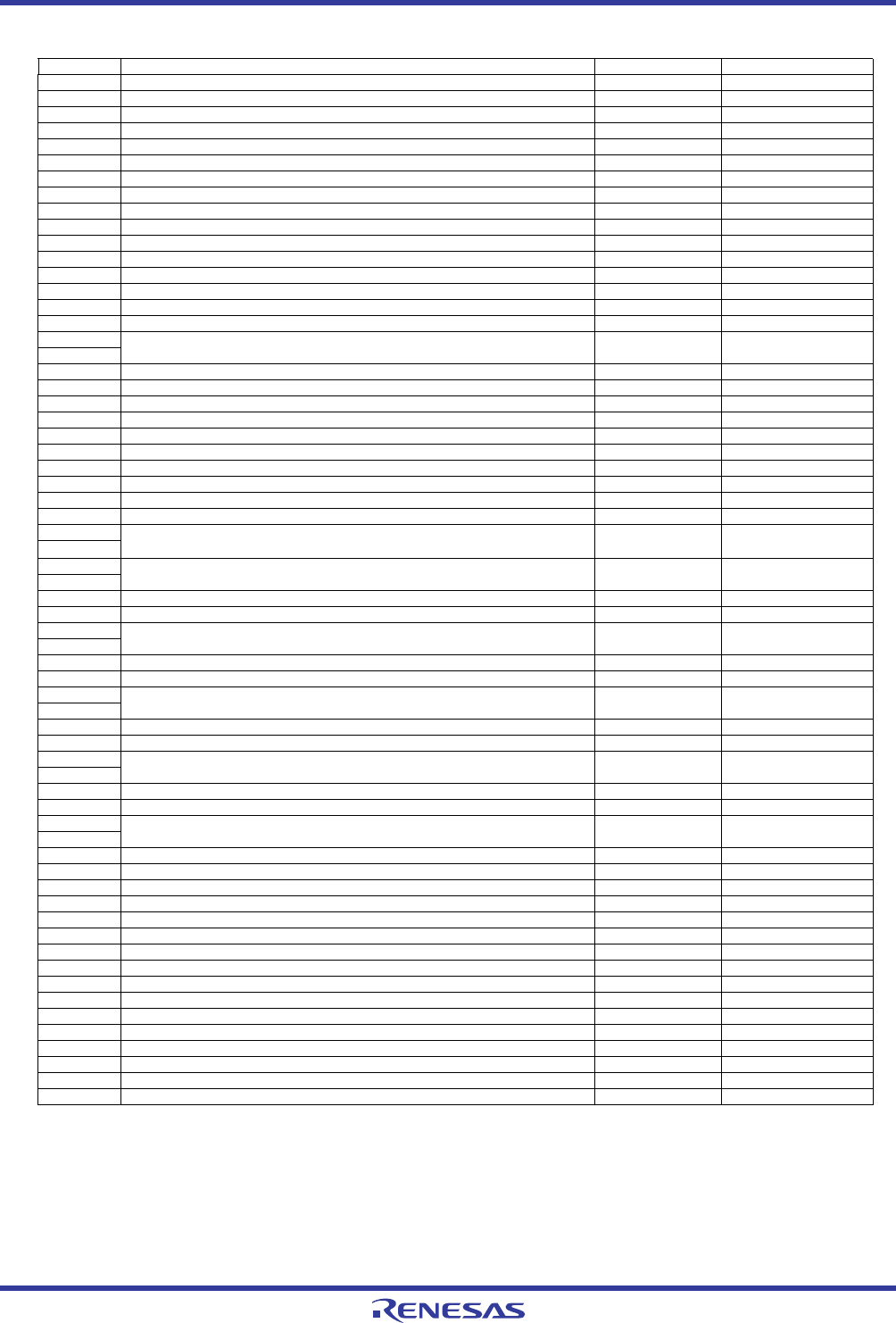

Table 4.3 SFR Information (3)

(1)

X: Undefined

NOTES:

1. The blank regions are reserved. Do not access locations in these regions.

2. When the output compare mode is selected (the TCC13 bit in the TCC1 register = 1), the value is set to FFFF

16.

Address Register Symbol After reset

0080h Timer Z Mode Register TZMR 00h

0081h

0082h

0083h

0084h Timer Z Waveform Output Control Register PUM 00h

0085h Prescaler Z Register PREZ FFh

0086h Timer Z Secondary Register TZSC FFh

0087h Timer Z Primary Register TZPR FFh

0088h

0089h

008Ah Timer Z Output Control Register TZOC 00h

008Bh Timer X Mode Register TXMR 00h

008Ch Prescaler X Register PREX FFh

008Dh Timer X Register TX FFh

008Eh Timer Count Source Setting Register TCSS 00h

008Fh

0090h Timer C Register TC 00h

0091h 00h

0092h

0093h

0094h

0095h

0096h External Input Enable Register INTEN 00h

0097h

0098h Key Input Enable Register KIEN 00h

0099h

009Ah Timer C Control Register 0 TCC0 00h

009Bh Timer C Control Register 1 TCC1 00h

009Ch Capture, Compare 0 Register TM0 00h

009Dh

00h

(2)

009Eh Compare 1 Register TM1 FFh

009Fh FFh

00A0h UART0 Transmit/Receive Mode Register U0MR 00h

00A1h UART0 Bit Rate Register U0BRG XXh

00A2h UART0 Transmit Buffer Register U0TB XXh

00A3h XXh

00A4h UART0 Transmit/Receive Control Register 0 U0C0 00001000b

00A5h UART0 Transmit/Receive Control Register 1 U0C1 00000010b

00A6h UART0 Receive Buffer Register U0RB XXh

00A7h XXh

00A8h UART1 Transmit/Receive Mode Register U1MR 00h

00A9h UART1 Bit Rate Register U1BRG XXh

00AAh UART1 Transmit Buffer Register U1TB XXh

00ABh XXh

00ACh UART1 Transmit/Receive Control Register 0 U1C0 00001000b

00ADh UART1 Transmit/Receive Control Register 1 U1C1 00000010b

00AEh UART1 Receive Buffer Register U1RB XXh

00AFh XXh

00B0h UART Transmit/Receive Control Register 2 UCON 00h

00B1h

00B2h

00B3h

00B4h

00B5h

00B6h

00B7h

00B8h

00B9h

00BAh

00BBh

00BCh

00BDh

00BEh

00BFh