Emulation Pod User's Manual

Table Of Contents

- Preface

- Contents

- 1. Precautions for Safety

- 2. Preparation

- 3. Setting Up

- 4. Usage

- 5. Specifications

- 6. Troubleshooting

- 6.1 Flowchart to Remedy the Troubles

- 6.2 When the Emulator Debugger Does Not Start Up Properly

- 6.3 Operation Differs from That of PROM Version MCUs

- (1) Does Not Operate with Operating Frequencies (3.6 V to 5.5 V) Properly

- (2) Does Not Operate with Operating Frequencies (2.7 V to 3.6 V) Properly

- (3) Cannot Reset from Target System

- (4) Data Values of ROM Area at Power-on Are Different

- (5) HOLD* control

- (6) A-D Conversion Values are Different from Expected Values

- (7) Outputs of ALE, Address and Others are Different from Those of Actual MCUs

- 7. Maintenance and Guarantee

( 55 / 78 )

(2) Separate Bus, With Wait, Accessing External Memory Area

Table 5.7 and Figure 5.7 show the bus timing in the memory expansion mode and the microprocessor

mode (with wait, accessing external memory area and using multiplex bus).

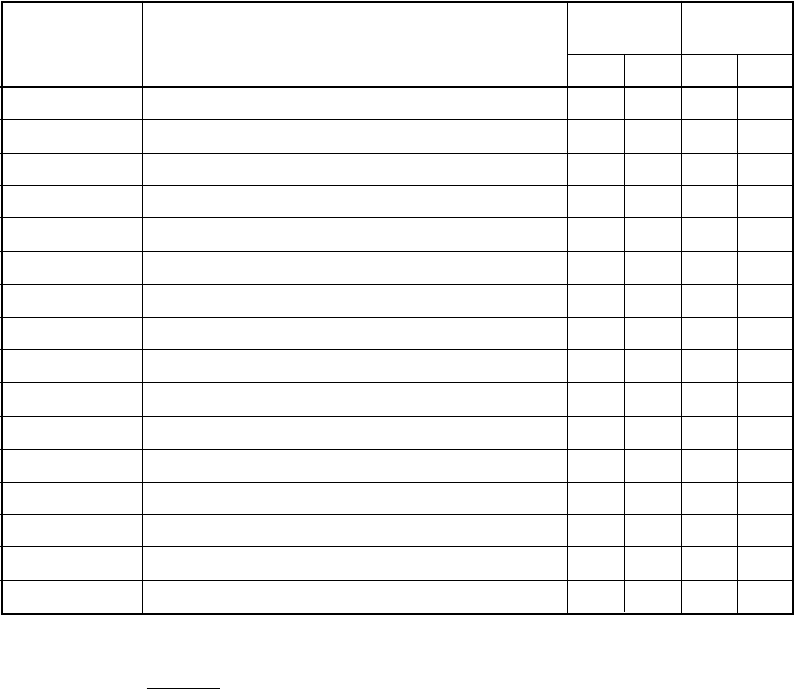

Table 5.7 Memory expansion mode and microprocessor mode (with wait, external memory area)

*1 Calculated by the following formula according to the frequency of BCLK.

Td (BCLK-AD)

Th (BCLK-AD)

Th (RD-AD)

Th (WR-AD)

Td (BCLK-CS)

Th (BCLK-CS)

Td (BCLK-ALE)

Th (BCLK-ALE)

Td (BCLK-RD)

Th (BCLK-RD)

Td (BCLK-WR)

Th (BCLK-WR)

Td (BCLK-DB)

Th (BCLK-DB)

Td (DB-WR)

Th (WR-DB)

Address output delay time

Address output hold time (BCLK standard)

Address output hold time (RD standard)

Address output hold time (WR standard)

Chip-select output delay time

Chip-select output hold time (BCLK standard)

ALE signal output delay time

ALE signal output hold time

RD signal output delay time

RD signal output hold time

WR signal output delay time

WR signal output hold time

Data output delay time (BCLK standard)

Data output hold time (BCLK standard)

Data output delay time (WR standard)

Data output hold time (WR standard)

Min.

4

0

0

4

-4

0

0

4

(*1)

0

Max.

60

60

60

60

60

80

Min. Max.

Actual MCU

[ns]

This product

[ns]

Symbol

Item

Td (DB-WR)=

10

9

f(BCLK)

-80 [ns]

See left

See left

See left

See left

See left

See left

See left

See left

See left

See left

See left

See left

See left

See left

See left

See left