User guide

Redpine Signals, Inc. Proprietary and Confidential. Page 114

R

R

S

S

9

9

1

1

1

1

0

0

-

-

N

N

-

-

1

1

1

1

-

-

2

2

2

2

/

/

2

2

4

4

/

/

2

2

8

8

S

S

o

o

f

f

t

t

w

w

a

a

r

r

e

e

P

P

r

r

o

o

g

g

r

r

a

a

m

m

m

m

i

i

n

n

g

g

R

R

e

e

f

f

e

e

r

r

e

e

n

n

c

c

e

e

M

M

a

a

n

n

u

u

a

a

l

l

V

V

e

e

r

r

s

s

i

i

o

o

n

n

4

4

.

.

1

1

5

5

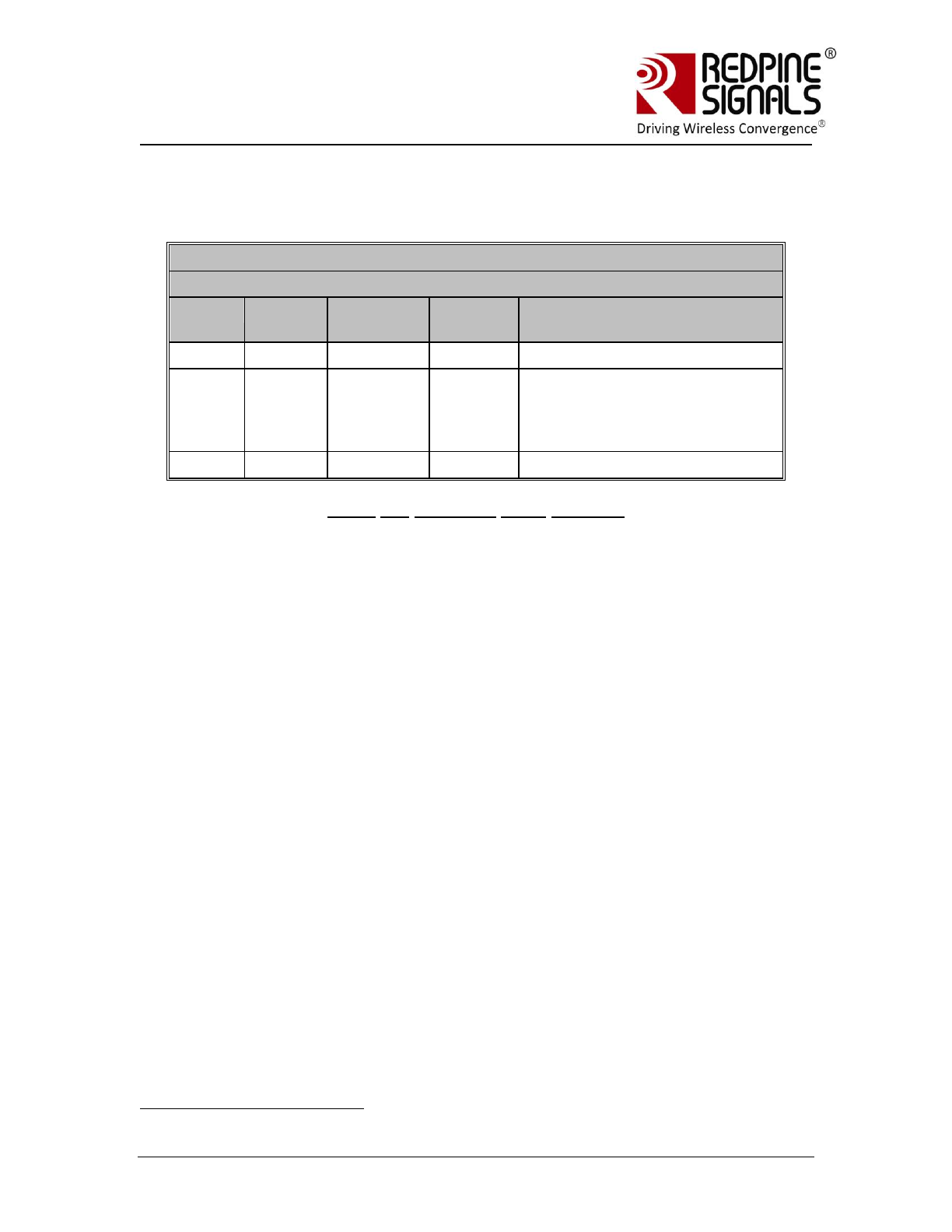

INTR_CLEAR

INTR_CLEAR

Base Address: 0x2200_0000, Offset Address: 0x10

Bit

Access

Function

Default

Value

Description

[7:6]

R

Reserved

0x0

Reserved for future use

5

R/W

POWER_M

ODE1

interrupt

clear

0x0

Writing a „1‟ to this bit clears

the interrupt raised by the

module due to this bit.

[4:0]

R/W

Reserved

0x0

Reserved for future use

Table 11: Interrupt Clear Register

Register Write

This is same as master write. The address to be supplied is 0x2200_0010. Bit

numbe5 can be set to „1‟ or „0‟ as desired, while the other bits should be set to

all „0‟ while writing.

Register Read

This is same as the master read. The address to be supplied is 0x2200_0010.

4.6 Power modes

1

The RS9110-N-11-2X module supports three power modes with the SPI

interface. The Host can switch among the power modes using the commands

depending on the Wi-Fi connection status as defined in this section.

The power modes supported by the RS9110-N-11-2X module for SPI interface

are classified based on the Host‟s capability to negotiate with RS9110-N-11-2X

and the Wi-Fi connection status.

4.6.1 Power mode 0

In this mode, power save is disabled in the RS9110-N-11-2X module. The

module will be in Power Mode 0 by default.

4.6.2 Power mode 1

The module can be configured for Power Mode 1 or Power Mode 2. The module

puts to sleep the Baseband and RF components between each DTIM, when there

is no traffic. In Power Mode 1, the module also powers off the Core Control Block

once it gets the indication from the Host. For this, the module first sends a sleep

request (it does this everytime it wakes after a DTIM) to the Host by asserting

interrupt line. After the host gets this interrupt, it reads the register

SPI_HOST_INTR using register read. If the bit 5 of that register is „1‟, it is

1

Not supported in ad-hoc mode