Datasheet

06 February 2012 Broadcom Europe Ltd. 406 Science Park Milton Road Cambridge CB4 0WW Page 202

© 2012 Broadcom Corporation. All rights reserved

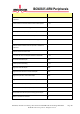

Feature/Parameter

Selected value

Width of Packet Counters

10

Remove Optional Features

0: No

Power

-

on Value of User ID Register

0x2708A000

Enable Power

Optimization

0: No

Is Minimum AHB Operating Frequency Less than 60 MHz

1: Yes

Reset Style of Clocked always Blocks in RTL

0: Asynchronous

Instantiate Double

-

Synchronization Flops

1: Yes

Enable Filter on “iddig” Signal from PHY

1: Yes

Enable Filter

on “vbus_valid” Signal from PHY

1: Yes

Enable Filter on “a_valid” Signal from PHY

1: Yes

Enable Filter on “b_valid” Signal from PHY

1: Yes

Enable Filter on “session_end” Signal from PHY

1: Yes

Direction of Endpoints

Mode is {IN and OUT} for all endpoin

ts

Largest Device Mode Periodic Tx Data FIFO n Depth

768 for all endpoints (Except 0)

Largest Device Mode IN Endpoint Tx FIFOn Depth (n = 0 to 15)

when using dynamic FIFO sizing

0=32

1..5=512

6,7=768

15.2 Extra / Adapted registers.

Besides the registers as specified in the documentation of Synopsys a number of extra registers

have been added. These control the Analogue USB Phy and the connections of the USB block

into the Video core bus structure. Also the USB_GAHBCFG register has an alternative

function for the bits [4:1].

Base Address of the USB block – 0x7E98_0000