Manual

DS26519 16-Port T1/E1/J1 Transceiver

19 of 310

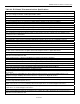

Figure 7-2. Detailed Block Diagram

CLOCK

SYNTHESIZ-

ER

MICROPROCESSOR

INTERFACE

JTAG

PORT

RESET

BLOCK

A[13:0]

D[7:0]

CSB

RDB/DSB

WRB/RWB

BTS

INTB

JTDI

JTMS

JTCLK

JTDO

JTRST

RESETB

MCLK

RCHBLK/CLKn

TCHBLK/CLKn

TCLKn

TSERn

TSYNCn

TSYSCLKn

RSYSCLKn

RSYNCn

RSERn

RCLKn

BPCLK1

REFCLKIO

TSSYNCIO

(Output Mode)

TTIPn

TRINGn

RRINGn

RTIPn

TSSYNCIO

(Input Mode)

Serial Interface Mode:

SPI

(SCLK, CPOL, CPHA,

SWAP, MOSI, and MISO)

RSIGn

RM/RFSYNCn

GPIOn

TSIGn

PRE-SCALER

PLL

SPI_SEL

RTIPEn

BPCLK2

CLKO

TRANSMIT

LIU

Waveform

Shaper/Line

Driver

RECEIVE

LIU

Clock/Data

Recovery

JITTER ATTENUATOR

TRANSMIT

ENABLE

Tx

BERT

Rx

BERT

Tx

HDLC

Rx

HDLC

Tx FRAMER:

System IF

B8ZS/

HDB3

Encode

Elastic

Store

Rx FRAMER:

System IF

B8ZS/

HDB3

Decode

Elastic

Store

ALB

LLB

FLB

RLB

PLB

DS26519

TRANSCEIVER 1 OF 16

BACKPLANE INTERFACE