User guide

Table Of Contents

- Features

- Pin Configurations

- Overview

- AVR CPU Core

- AVR ATmega162 Memories

- System Clock and Clock Options

- Power Management and Sleep Modes

- System Control and Reset

- Interrupts

- I/O-Ports

- Introduction

- Ports as General Digital I/O

- Alternate Port Functions

- Register Description for I/O-Ports

- Port A Data Register – PORTA

- Port A Data Direction Register – DDRA

- Port A Input Pins Address – PINA

- Port B Data Register – PORTB

- Port B Data Direction Register – DDRB

- Port B Input Pins Address – PINB

- Port C Data Register – PORTC

- Port C Data Direction Register – DDRC

- Port C Input Pins Address – PINC

- Port D Data Register – PORTD

- Port D Data Direction Register – DDRD

- Port D Input Pins Address – PIND

- Port E Data Register – PORTE

- Port E Data Direction Register – DDRE

- Port E Input Pins Address – PINE

- External Interrupts

- 8-bit Timer/Counter0 with PWM

- Timer/Counter0, Timer/Counter1, and Timer/Counter3 Prescalers

- 16-bit Timer/Counter (Timer/Counter1 and Timer/Counter3)

- Restriction in ATmega161 Compatibility Mode

- Overview

- Accessing 16-bit Registers

- Timer/Counter Clock Sources

- Counter Unit

- Input Capture Unit

- Output Compare Units

- Compare Match Output Unit

- Modes of Operation

- Timer/Counter Timing Diagrams

- 16-bit Timer/Counter Register Description

- Timer/Counter1 Control Register A – TCCR1A

- Timer/Counter3 Control Register A – TCCR3A

- Timer/Counter1 Control Register B – TCCR1B

- Timer/Counter3 Control Register B – TCCR3B

- Timer/Counter1 – TCNT1H and TCNT1L

- Timer/Counter3 – TCNT3H and TCNT3L

- Output Compare Register 1 A – OCR1AH and OCR1AL

- Output Compare Register 1 B – OCR1BH and OCR1BL

- Output Compare Register 3 A – OCR3AH and OCR3AL

- Output Compare Register 3 B – OCR3BH and OCR3BL

- Input Capture Register 1 – ICR1H and ICR1L

- Input Capture Register 3 – ICR3H and ICR3L

- Timer/Counter Interrupt Mask Register – TIMSK(1)

- Extended Timer/Counter Interrupt Mask Register – ETIMSK(1)

- Timer/Counter Interrupt Flag Register – TIFR(1)

- Extended Timer/Counter Interrupt Flag Register – ETIFR(1)

- 8-bit Timer/Counter2 with PWM and Asynchronous operation

- Serial Peripheral Interface – SPI

- USART

- Analog Comparator

- JTAG Interface and On-chip Debug System

- IEEE 1149.1 (JTAG) Boundary-scan

- Boot Loader Support – Read-While-Write Self-programming

- Features

- Application and Boot Loader Flash Sections

- Read-While-Write and No Read-While-Write Flash Sections

- Boot Loader Lock Bits

- Entering the Boot Loader Program

- Addressing the Flash During Self- programming

- Self-programming the Flash

- Performing Page Erase by SPM

- Filling the Temporary Buffer (Page Loading)

- Performing a Page Write

- Using the SPM Interrupt

- Consideration while Updating BLS

- Prevent Reading the RWW Section During Self- programming

- Setting the Boot Loader Lock Bits by SPM

- EEPROM Write Prevents Writing to SPMCR

- Reading the Fuse and Lock Bits from Software

- Preventing Flash Corruption

- Programming Time for Flash When Using SPM

- Simple Assembly Code Example for a Boot Loader

- ATmega162 Boot Loader Parameters

- Memory Programming

- Program And Data Memory Lock Bits

- Fuse Bits

- Signature Bytes

- Calibration Byte

- Parallel Programming Parameters, Pin Mapping, and Commands

- Parallel Programming

- Enter Programming Mode

- Considerations for Efficient Programming

- Chip Erase

- Programming the Flash

- Programming the EEPROM

- Reading the Flash

- Reading the EEPROM

- Programming the Fuse Low Bits

- Programming the Fuse High Bits

- Programming the Extended Fuse Bits

- Programming the Lock Bits

- Reading the Fuse and Lock Bits

- Reading the Signature Bytes

- Reading the Calibration Byte

- Parallel Programming Characteristics

- Serial Downloading

- SPI Serial Programming Pin Mapping

- Programming via the JTAG Interface

- Programming Specific JTAG Instructions

- AVR_RESET (0xC)

- PROG_ENABLE (0x4)

- PROG_COMMANDS (0x5)

- PROG_PAGELOAD (0x6)

- PROG_PAGEREAD (0x7)

- Data Registers

- Reset Register

- Programming Enable Register

- Programming Command Register

- Virtual Flash Page Load Register

- Virtual Flash Page Read Register

- Programming Algorithm

- Entering Programming Mode

- Leaving Programming Mode

- Performing Chip Erase

- Programming the Flash

- Reading the Flash

- Programming the EEPROM

- Reading the EEPROM

- Programming the Fuses

- Programming the Lock Bits

- Reading the Fuses and Lock Bits

- Reading the Signature Bytes

- Reading the Calibration Byte

- Electrical Characteristics

- ATmega162 Typical Characteristics

- Active Supply Current

- Idle Supply Current

- Power-down Supply Current

- Power-save Supply Current

- Standby Supply Current

- Pin Pull-up

- Pin Driver Strength

- Pin Thresholds and Hysteresis

- BOD Thresholds and Analog Comparator Offset

- Internal Oscillator Speed

- Current Consumption of Peripheral Units

- Current Consumption in Reset and Reset Pulsewidth

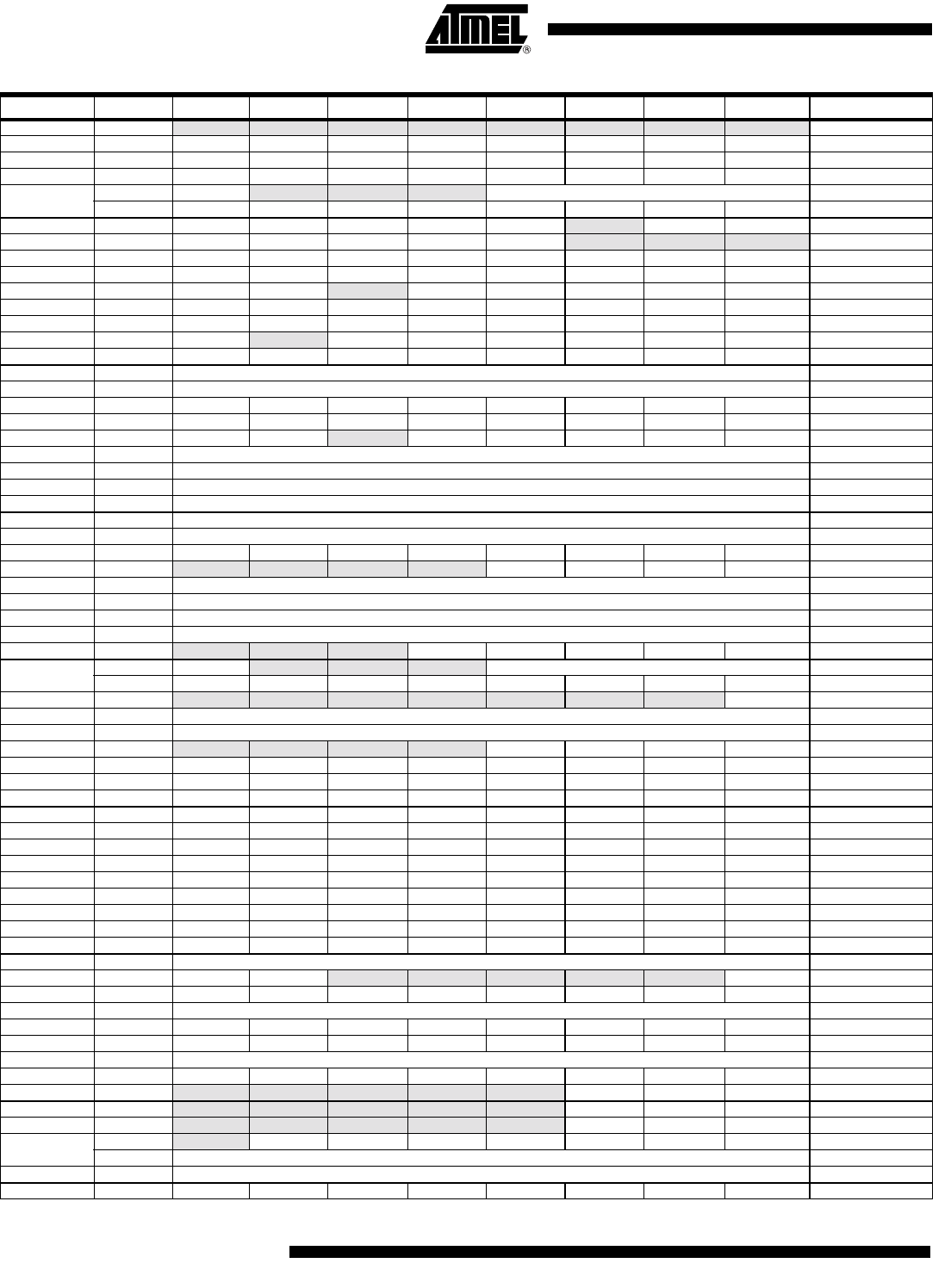

- Register Summary

- Instruction Set Summary

- Ordering Information

- Packaging Information

- Erratas

- Datasheet Change Log for ATmega162

- Table of Contents

304

ATmega162/V

2513E–AVR–09/03

(0x60) Reserved – – – – – – – –

0x3F (0x5F) SREG I T H S V N Z C 8

0x3E (0x5E) SPH SP15 SP14 SP13 SP12 SP11 SP10 SP9 SP8 11

0x3D (0x5D) SPL SP7 SP6 SP5 SP4 SP3 SP2 SP1 SP0 11

0x3C

(2)

(0x5C)

(2)

UBRR1H URSEL1

UBRR1[11:8]

189

UCSR1C URSEL1 UMSEL1 UPM11 UPM10 USBS1 UCSZ11 UCSZ10 UCPOL1 188

0x3B (0x5B) GICR INT1 INT0 INT2 PCIE1 PCIE0

– IVSEL IVCE 60, 85

0x3A (0x5A) GIFR INTF1 INTF0 INTF2 PCIF1 PCIF0

– – –86

0x39 (0x59) TIMSK TOIE1 OCIE1A OCIE1B OCIE2 TICIE1 TOIE2 TOIE0 OCIE0 101, 133, 154

0x38 (0x58) TIFR TOV1 OCF1A OCF1B OCF2 ICF1 TOV2 TOV0 OCF0 102, 135, 155

0x37 (0x57) SPMCR SPMIE RWWSB

– RWWSRE BLBSET PGWRT PGERS SPMEN 220

0x36 (0x56) EMCUCR SM0 SRL2 SRL1 SRL0 SRW01 SRW00 SRW11 ISC2 28,42,84

0x35 (0x55) MCUCR SRE SRW10 SE SM1 ISC11 ISC10 ISC01 ISC00 28,41,83

0x34 (0x54) MCUCSR JTD

– SM2 JTRF WDRF BORF EXTRF PORF 41,50,206

0x33 (0x53) TCCR0 FOC0 WGM00 COM01 COM00 WGM01 CS02 CS01 CS00 99

0x32 (0x52) TCNT0 Timer/Counter0 (8 Bits) 101

0x31 (0x51)

OCR0 Timer/Counter0 Output Compare Register 101

0x30 (0x50) SFIOR TSM XMBK XMM2 XMM1 XMM0 PUD PSR2 PSR310 30,69,104,156

0x2F (0x4F) TCCR1A COM1A1 COM1A0 COM1B1 COM1B0 FOC1A FOC1B WGM11 WGM10 127

0x2E (0x4E) TCCR1B ICNC1 ICES1

– WGM13 WGM12 CS12 CS11 CS10 130

0x2D (0x4D) TCNT1H Timer/Counter1 – Counter Register High Byte 132

0x2C (0x4C) TCNT1L Timer/Counter1 – Counter Register Low Byte 132

0x2B (0x4B) OCR1AH Timer/Counter1 – Output Compare Register A High Byte 132

0x2A (0x4A) OCR1AL Timer/Counter1 – Output Compare Register A Low Byte 132

0x29 (0x49) OCR1BH Timer/Counter1 – Output Compare Register B High Byte 132

0x28 (0x48) OCR1BL Timer/Counter1 – Output Compare Register B Low Byte 132

0x27 (0x47) TCCR2 FOC2 WGM20 COM21 COM20 WGM21 CS22 CS21 CS20 148

0x26 (0x46) ASSR

– – – – AS2 TCON2UB OCR2UB TCR2UB 152

0x25 (0x45) ICR1H Timer/Counter1 – Input Capture Register High Byte 133

0x24 (0x44) ICR1L Timer/Counter1 – Input Capture Register Low Byte 133

0x23 (0x43) TCNT2 Timer/Counter2 (8 Bits) 151

0x22 (0x42) OCR2 Timer/Counter2 Output Compare Register 151

0x21 (0x41) WDTCR

– – – WDCE WDE WDP2 WDP1 WDP0 52

0x20

(2)

(0x40)

(2)

UBRR0H URSEL0 – – – UBRR0[11:8] 189

UCSR0C URSEL0 UMSEL0 UPM01 UPM00 USBS0 UCSZ01 UCSZ00 UCPOL0 188

0x1F (0x3F) EEARH

– – – – – – – EEAR8 18

0x1E (0x3E) EEARL EEPROM Address Register Low Byte 18

0x1D (0x3D) EEDR EEPROM Data Register 19

0x1C (0x3C) EECR

– – – – EERIE EEMWE EEWE EERE 19

0x1B (0x3B) PORTA PORTA7 PORTA6 PORTA5 PORTA4 PORTA3 PORTA2 PORTA1 PORTA0 81

0x1A (0x3A) DDRA DDA7 DDA6 DDA5 DDA4 DDA3 DDA2 DDA1 DDA0 81

0x19 (0x39) PINA PINA7 PINA6 PINA5 PINA4 PINA3 PINA2 PINA1 PINA0 81

0x18 (0x38) PORTB PORTB7 PORTB6 PORTB5 PORTB4 PORTB3 PORTB2 PORTB1 PORTB0 81

0x17 (0x37) DDRB DDB7 DDB6 DDB5 DDB4 DDB3 DDB2 DDB1 DDB0 81

0x16 (0x36) PINB PINB7 PINB6 PINB5 PINB4 PINB3 PINB2 PINB1 PINB0 81

0x15 (0x35) PORTC PORTC7 PORTC6 PORTC5 PORTC4 PORTC3 PORTC2 PORTC1 PORTC0 81

0x14 (0x34) DDRC DDC7 DDC6 DDC5 DDC4 DDC3 DDC2 DDC1 DDC0 81

0x13 (0x33) PINC PINC7 PINC6 PINC5 PINC4 PINC3 PINC2 PINC1 PINC0 82

0x12 (0x32) PORTD PORTD7 PORTD6 PORTD5 PORTD4 PORTD3 PORTD2 PORTD1 PORTD0 82

0x11 (0x31) DDRD DDD7 DDD6 DDD5 DDD4 DDD3 DDD2 DDD1 DDD0 82

0x10 (0x30) PIND PIND7 PIND6 PIND5 PIND4 PIND3 PIND2 PIND1 PIND0 82

0x0F (0x2F) SPDR SPI Data Register 163

0x0E (0x2E) SPSR SPIF WCOL

– – – – – SPI2X 163

0x0D (0x2D) SPCR SPIE SPE DORD MSTR CPOL CPHA SPR1 SPR0 161

0x0C (0x2C) UDR0 USART0 I/O Data Register 185

0x0B (0x2B) UCSR0A RXC0 TXC0 UDRE0 FE0 DOR0 UPE0 U2X0 MPCM0 185

0x0A (0x2A) UCSR0B RXCIE0 TXCIE0 UDRIE0 RXEN0 TXEN0 UCSZ02 RXB80 TXB80 186

0x09 (0x29) UBRR0L USART0 Baud Rate Register Low Byte 189

0x08 (0x28) ACSR ACD ACBG ACO ACI ACIE ACIC ACIS1 ACIS0 194

0x07 (0x27) PORTE

– – – – – PORTE2 PORTE1 PORTE0 82

0x06 (0x26) DDRE

– – – – – DDE2 DDE1 DDE0 82

0x05 (0x25) PINE

– – – – – PINE2 PINE1 PINE0 82

0x04

(1)

(0x24)

(1)

OSCCAL – CAL6 CAL5 CAL4 CAL3 CAL2 CAL1 CAL0 37

OCDR On-chip Debug Register 201

0x03 (0x23) UDR1 USART1 I/O Data Register 185

0x02 (0x22) UCSR1A RXC1 TXC1 UDRE1 FE1 DOR1 UPE1 U2X1 MPCM1 185

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Page