User guide

Table Of Contents

- Features

- Pin Configurations

- Overview

- AVR CPU Core

- AVR ATmega162 Memories

- System Clock and Clock Options

- Power Management and Sleep Modes

- System Control and Reset

- Interrupts

- I/O-Ports

- Introduction

- Ports as General Digital I/O

- Alternate Port Functions

- Register Description for I/O-Ports

- Port A Data Register – PORTA

- Port A Data Direction Register – DDRA

- Port A Input Pins Address – PINA

- Port B Data Register – PORTB

- Port B Data Direction Register – DDRB

- Port B Input Pins Address – PINB

- Port C Data Register – PORTC

- Port C Data Direction Register – DDRC

- Port C Input Pins Address – PINC

- Port D Data Register – PORTD

- Port D Data Direction Register – DDRD

- Port D Input Pins Address – PIND

- Port E Data Register – PORTE

- Port E Data Direction Register – DDRE

- Port E Input Pins Address – PINE

- External Interrupts

- 8-bit Timer/Counter0 with PWM

- Timer/Counter0, Timer/Counter1, and Timer/Counter3 Prescalers

- 16-bit Timer/Counter (Timer/Counter1 and Timer/Counter3)

- Restriction in ATmega161 Compatibility Mode

- Overview

- Accessing 16-bit Registers

- Timer/Counter Clock Sources

- Counter Unit

- Input Capture Unit

- Output Compare Units

- Compare Match Output Unit

- Modes of Operation

- Timer/Counter Timing Diagrams

- 16-bit Timer/Counter Register Description

- Timer/Counter1 Control Register A – TCCR1A

- Timer/Counter3 Control Register A – TCCR3A

- Timer/Counter1 Control Register B – TCCR1B

- Timer/Counter3 Control Register B – TCCR3B

- Timer/Counter1 – TCNT1H and TCNT1L

- Timer/Counter3 – TCNT3H and TCNT3L

- Output Compare Register 1 A – OCR1AH and OCR1AL

- Output Compare Register 1 B – OCR1BH and OCR1BL

- Output Compare Register 3 A – OCR3AH and OCR3AL

- Output Compare Register 3 B – OCR3BH and OCR3BL

- Input Capture Register 1 – ICR1H and ICR1L

- Input Capture Register 3 – ICR3H and ICR3L

- Timer/Counter Interrupt Mask Register – TIMSK(1)

- Extended Timer/Counter Interrupt Mask Register – ETIMSK(1)

- Timer/Counter Interrupt Flag Register – TIFR(1)

- Extended Timer/Counter Interrupt Flag Register – ETIFR(1)

- 8-bit Timer/Counter2 with PWM and Asynchronous operation

- Serial Peripheral Interface – SPI

- USART

- Analog Comparator

- JTAG Interface and On-chip Debug System

- IEEE 1149.1 (JTAG) Boundary-scan

- Boot Loader Support – Read-While-Write Self-programming

- Features

- Application and Boot Loader Flash Sections

- Read-While-Write and No Read-While-Write Flash Sections

- Boot Loader Lock Bits

- Entering the Boot Loader Program

- Addressing the Flash During Self- programming

- Self-programming the Flash

- Performing Page Erase by SPM

- Filling the Temporary Buffer (Page Loading)

- Performing a Page Write

- Using the SPM Interrupt

- Consideration while Updating BLS

- Prevent Reading the RWW Section During Self- programming

- Setting the Boot Loader Lock Bits by SPM

- EEPROM Write Prevents Writing to SPMCR

- Reading the Fuse and Lock Bits from Software

- Preventing Flash Corruption

- Programming Time for Flash When Using SPM

- Simple Assembly Code Example for a Boot Loader

- ATmega162 Boot Loader Parameters

- Memory Programming

- Program And Data Memory Lock Bits

- Fuse Bits

- Signature Bytes

- Calibration Byte

- Parallel Programming Parameters, Pin Mapping, and Commands

- Parallel Programming

- Enter Programming Mode

- Considerations for Efficient Programming

- Chip Erase

- Programming the Flash

- Programming the EEPROM

- Reading the Flash

- Reading the EEPROM

- Programming the Fuse Low Bits

- Programming the Fuse High Bits

- Programming the Extended Fuse Bits

- Programming the Lock Bits

- Reading the Fuse and Lock Bits

- Reading the Signature Bytes

- Reading the Calibration Byte

- Parallel Programming Characteristics

- Serial Downloading

- SPI Serial Programming Pin Mapping

- Programming via the JTAG Interface

- Programming Specific JTAG Instructions

- AVR_RESET (0xC)

- PROG_ENABLE (0x4)

- PROG_COMMANDS (0x5)

- PROG_PAGELOAD (0x6)

- PROG_PAGEREAD (0x7)

- Data Registers

- Reset Register

- Programming Enable Register

- Programming Command Register

- Virtual Flash Page Load Register

- Virtual Flash Page Read Register

- Programming Algorithm

- Entering Programming Mode

- Leaving Programming Mode

- Performing Chip Erase

- Programming the Flash

- Reading the Flash

- Programming the EEPROM

- Reading the EEPROM

- Programming the Fuses

- Programming the Lock Bits

- Reading the Fuses and Lock Bits

- Reading the Signature Bytes

- Reading the Calibration Byte

- Electrical Characteristics

- ATmega162 Typical Characteristics

- Active Supply Current

- Idle Supply Current

- Power-down Supply Current

- Power-save Supply Current

- Standby Supply Current

- Pin Pull-up

- Pin Driver Strength

- Pin Thresholds and Hysteresis

- BOD Thresholds and Analog Comparator Offset

- Internal Oscillator Speed

- Current Consumption of Peripheral Units

- Current Consumption in Reset and Reset Pulsewidth

- Register Summary

- Instruction Set Summary

- Ordering Information

- Packaging Information

- Erratas

- Datasheet Change Log for ATmega162

- Table of Contents

123

ATmega162/V

2513E–AVR–09/03

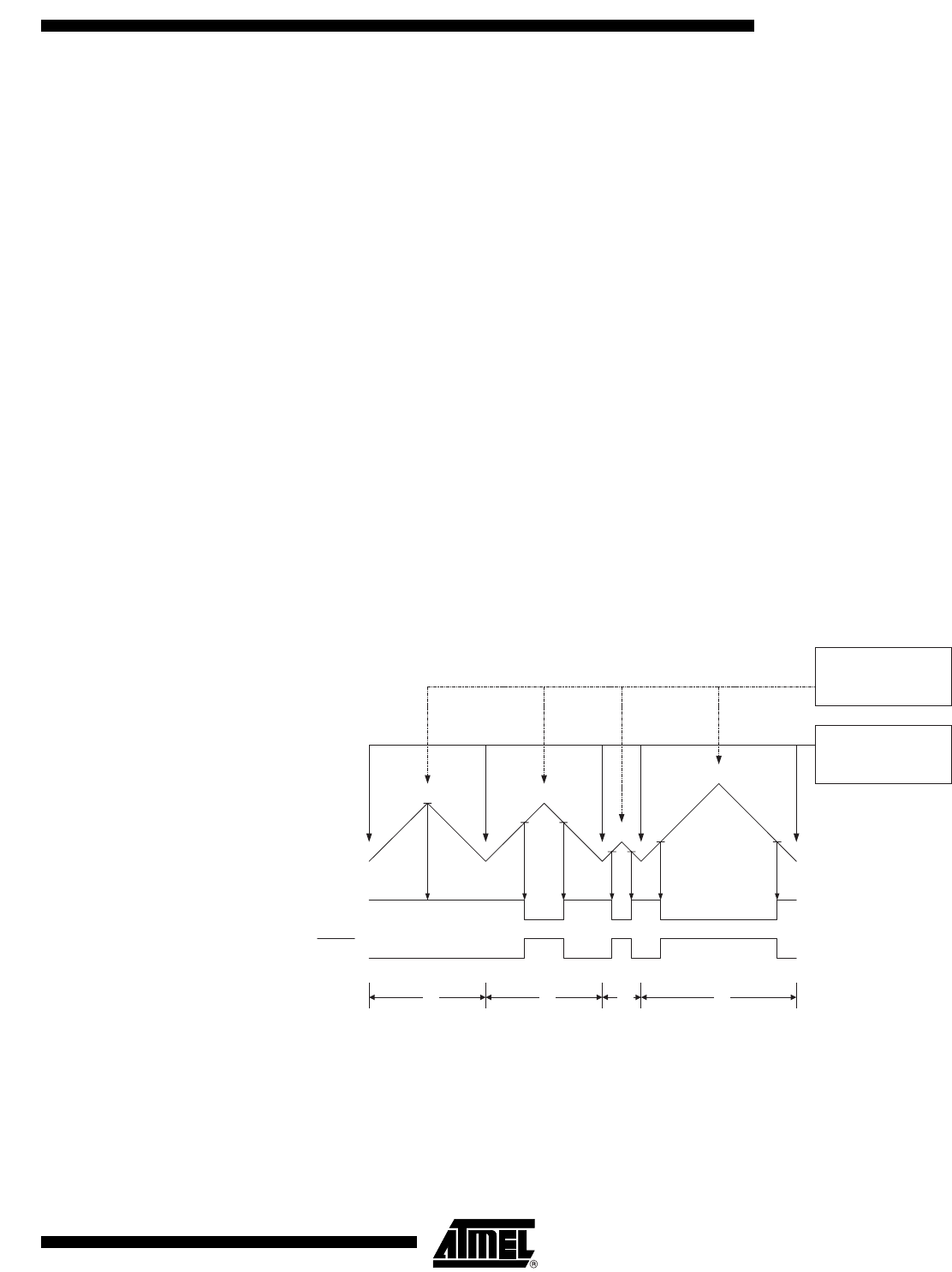

pared to the single-slope operation. However, due to the symmetric feature of the dual-

slope PWM modes, these modes are preferred for motor control applications.

The main difference between the phase correct, and the phase and frequency correct

PWM mode is the time the OCRnx Register is updated by the OCRnx Buffer Register,

(see Figure 53 and Figure 54).

The PWM resolution for the phase and frequency correct PWM mode can be defined by

either ICRn or OCRnA. The minimum resolution allowed is 2-bit (ICRn or OCRnA set to

0x0003), and the maximum resolution is 16-bit (ICRn or OCRnA set to MAX). The PWM

resolution in bits can be calculated using the following equation:

In phase and frequency correct PWM mode the counter is incremented until the counter

value matches either the value in ICRn (WGMn3:0 = 8), or the value in OCRnA

(WGMn3:0 = 9). The counter has then reached the TOP and changes the count direc-

tion. The TCNTn value will be equal to TOP for one timer clock cycle. The timing

diagram for the phase correct and frequency correct PWM mode is shown on Figure 54.

The figure shows phase and frequency correct PWM mode when OCRnA or ICRn is

used to define TOP. The TCNTn value is in the timing diagram shown as a histogram for

illustrating the dual-slope operation. The diagram includes non-inverted and inverted

PWM outputs. The small horizontal line marks on the TCNTn slopes represent compare

matches between OCRnx and TCNTn. The OCnx Interrupt Flag will be set when a Com-

pare Match occurs.

Figure 54. Phase and Frequency Correct PWM Mode, Timing Diagram

The Timer/Counter Overflow Flag (TOVn) is set at the same timer clock cycle as the

OCRnx Registers are updated with the double buffer value (at BOTTOM). When either

OCRnA or ICRn is used for defining the TOP value, the OCnA or ICFn Flag set when

TCNTn has reached TOP. The Interrupt Flags can then be used to generate an interrupt

each time the counter reaches the TOP or BOTTOM value.

When changing the TOP value the program must ensure that the new TOP value is

higher or equal to the value of all of the compare registers. If the TOP value is lower

R

PFCPWM

TOP 1+()log

2()log

-----------------------------------=

OCRnx/TOP Update and

TOVn Interrupt Flag Set

(Interrupt on Bottom)

OCnA Interrupt Flag Set

or ICFn Interrupt Flag Set

(Interrupt on TOP)

1 2 3 4

TCNTn

Period

OCnx

OCnx

(COMnx1:0 = 2)

(COMnx1:0 = 3)