Manual

Table Of Contents

- Ordering Information

- Features

- Description

- Architectural Overview

- General Purpose Register File

- ALU - Arithmetic Logic Unit

- ISP Flash Program Memory

- SRAM Data Memory

- Program and Data Addressing Modes

- Register Direct, Single Register Rd

- Register Direct, Two Registers Rd and Rr

- I/O Direct

- Data Direct

- Data Indirect with Displacement

- Data Indirect

- Data Indirect With Pre-Decrement

- Data Indirect With Post-Increment

- Constant Addressing Using the LPM and ELPM Instructions

- Direct Program Address, JMP and CALL

- Indirect Program Addressing, IJMP and ICALL

- Relative Program Addressing, RJMP and RCALL

- EEPROM Data Memory

- Memory Access Times and Instruction Execution Timing

- I/O Memory

- Reset and Interrupt Handling

- Reset Sources

- Power-On Reset

- External Reset

- Watchdog Reset

- MCU Status Register - MCUSR

- Interrupt Handling

- External Interrupt Mask Register - EIMSK

- External Interrupt Flag Register - EIFR

- External Interrupt Control Register - EICR

- Timer/Counter Interrupt Mask Register - TIMSK

- Timer/Counter Interrupt Flag Register - TIFR

- Interrupt Response Time

- Sleep Modes

- Timer/Counters

- Timer/Counter Prescalers

- 8-bit Timer/Counters T/C0 and T/C2

- Timer/Counter0 Control Register - TCCR0

- Timer/Counter2 Control Register - TCCR2

- Timer/Counter0 - TCNT0

- Timer/Counter2 - TCNT2

- Timer/Counter0 Output Compare Register - OCR0

- Timer/Counter2 Output Compare Register - OCR2

- Timer/Counter 0 and 2 in PWM mode

- Asynchronous Status Register - ASSR

- Asynchronous Operation of Timer/Counter0

- 16-bit Timer/Counter1

- Timer/Counter1 Control Register A - TCCR1A

- Timer/Counter1 Control Register B - TCCR1B

- Timer/Counter1 - TCNT1H and TCNT1L

- Timer/Counter1 Output Compare Register - OCR1AH and OCR1AL

- Timer/Counter1 Output Compare Register - OCR1BH and OCR1BL

- Timer/Counter1 Input Capture Register - ICR1H and ICR1L

- Timer/Counter1 in PWM mode

- Watchdog Timer

- EEPROM Read/Write Access

- Serial Peripheral Interface - SPI

- UART

- Analog Comparator

- Analog to Digital Converter

- Interface to external SRAM

- I/O-Ports

- Memory Programming

- Electrical Characteristics

- Typical characteristics

- Register Summary

- Instruction Set Summary (Continued)

ATmega603/103

3

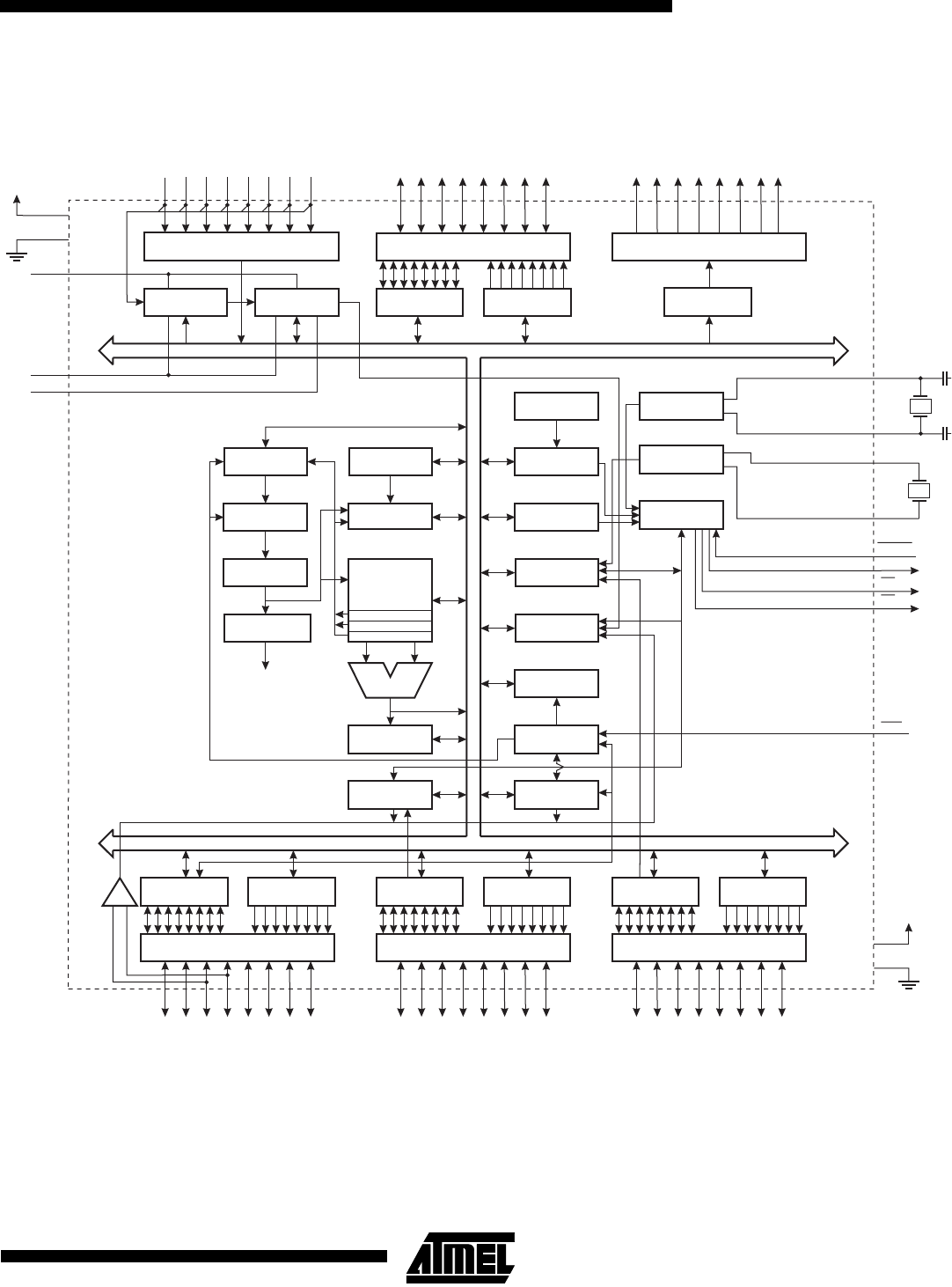

Block Diagram

Figure 1. The ATmega603/103 Block Diagram

PROGRAM

COUNTER

INTERNAL

OSCILLATOR

WATCHDOG

TIMER

STACK

POINTER

PROGRAM

FLASH

MCU CONTROL

REGISTER

SRAM

GENERAL

PURPOSE

REGISTERS

INSTRUCTION

REGISTER

TIMER/

COUNTERS

INSTRUCTION

DECODER

DATA DIR.

REG. PORTB

DATA DIR.

REG. PORTE

DATA DIR.

REG. PORTA

DATA DIR.

REG. PORTD

DATA REGISTER

PORTB

DATA REGISTER

PORTE

DATA REGISTER

PORTA

DATA REGISTER

PORTC

DATA REGISTER

PORTD

PROGRAMMING

LOGIC

TIMING AND

CONTROL

OSCILLATOR

OSCILLATOR

INTERRUPT

UNIT

EEPROM

SPI

UART

STATUS

REGISTER

Z

Y

X

ALU

PORTB DRIVER/BUFFERSPORTE DRIVER/BUFFERS

PORTA DRIVER/BUFFERS

PORTF BUFFERS

ANALOG MUX ADC

PORTD DRIVER/BUFFERS

PORTC DRIVERS

PB0 PB7PE0 PE7

RESET

VCC

VCC

AGND

GND

GND

AREF

TOSC2

TOSC1

XTAL1

XTAL1

CONTROL

LINES

+

-

ANALOG

COMPARATOR

PD0 PD7

PEN

ALE

WR

RD

8-BIT DATA BUS

AVCC