Technical data

Publication No. 980673-067 Rev. B 1260-43 User Manual

Astronics Test Systems Module Operation 3-3

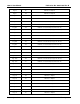

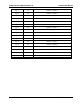

205801 Control Register 0

205803 Control Register 1

Table 3-1

shows the address offset assignments for each

Control/Status register while Table 3-2 shows the Control/Status

Register Relay / Buss Assignments. Refer to Appendix A and B

in determining relay groups and the relay reference designations.

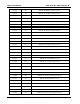

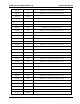

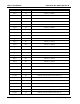

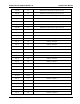

Table 3-1, Control/ Status Register Address Offset Assignments

Control/Status

Address

Function

Reg. 00A 001 Input Bus to Matrix Bus ‘A’ (lower bus bits 4-0)

Reg. 00B 003 Input Bus to Matrix Bus ‘A’ (upper bus bits 9-5)

Reg. 01A 005 Bypass Matrix Bus ‘A’ to Internal Bus ‘B’ (lower bus bits 4-0)

Reg. 01B 007 Bypass Matrix Bus ‘A’ to Internal Bus ‘B’ (upper bus bits 9-5)

Reg. 02A 009 Internal Bus ‘B’ to Matrix Bus ‘B’ (lower bus bits 4-0)

Reg. 02B 00B Internal Bus ‘B’ to Matrix Bus ‘B’ (upper bus bits 9-5)

Reg. 03A 00D Bypass Matrix Bus ‘B’ to Internal Bus ‘C’ (lower bus bits 4-0)

Reg. 03B 00F Bypass Matrix Bus ‘B’ to Internal Bus ‘C’ (upper bus bits 9-5)

Reg. 04A 011 Internal Bus ‘C’ to Matrix Bus ‘C’ (lower bus bits 4-0)

Reg. 04B 013 Internal Bus ‘C’ to Matrix Bus ‘C’ (upper bus bits 9-5)

Reg. 05A 015 Bypass Matrix Bus ‘C’ to Output Bus (lower bus bits 4-0)

Reg. 05B 017 Bypass Matrix Bus ‘C’ to Output Bus (upper bus bits 9-5)

Reg. 06A 019 Matrix Bus ‘A’ Stub Break 1 (lower bus bits 4-0)

Reg. 06B 01B Matrix Bus ‘A’ Stub Break 1 (upper bus bits 9-5)

Reg. 07A 01D Matrix Bus ‘A’ Stub Break 2 (lower bus bits 4-0)

Reg. 07B 01F Matrix Bus ‘A’ Stub Break 2 (upper bus bits 9-5)

Reg. 08A 021 Matrix Bus ‘A’ Stub Break 3 (lower bus bits 4-0)

Reg. 08B 023 Matrix Bus ‘A’ Stub Break 3 (upper bus bits 9-5)

Reg. 09A 025 Matrix Bus ‘A’ Stub Break 4 (lower bus bits 4-0)

Reg. 09B 027 Matrix Bus ‘A’ Stub Break 4 (upper bus bits 9-5)

Reg. 10A 029 Matrix Bus ‘B’ Stub Break 1 (lower bus bits 4-0)