Datasheet

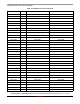

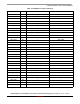

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29

A VSS_MAIN

DDR_DCF1

8

DDR_CK1_

P

DDR_DCF2

6

PCIE_CTR

L0_PERST

_B

PCIE0_TX0

_P

PCIE0_RX0

_P

USB_OTG1

_ID

USB_OTG1

_DP

EMMC0_D

ATA0

ENET0_RG

MII_RXC

ENET0_MD

C

VSS_MAIN

B

DDR_DCF0

1

DDR_DCF0

7

DDR_DCF1

7

DDR_CK1_

N

DDR_DCF2

1

PCIE0_TX0

_N

PCIE_CTR

L0_W AKE_

B

PCIE0_RX0

_N

USB_OTG1

_DN

EMMC0_R

ESET_B

ENET0_RG

MII_TXD3

ENET0_RG

MII_RXD3

ESAI0_FSR

ESAI0_TX4

_RX1

C VSS_MAIN VSS_MAIN VSS_MAIN VSS_MAIN VSS_MAIN VSS_MAIN

PCIE_REF

CLK100M_

N

VSS_MAIN VSS_MAIN

VDD_EMM

C0_VSELE

CT_1P8_3

P3

ENET0_RG

MII_TXD1

ENET0_RG

MII_RXD0

ESAI0_SCK

T

ESAI0_TX2

_RX3

VSS_MAIN

D

DDR_DCF1

2

DDR_DCF0

5

DDR_DCF2

0

DDR_DCF2

9

DDR_DCF2

8

VDD_USB_

3P3

PCIE_REF

CLK100M_

P

VDD_USB_

SS3_LDO_

1P0_CAP

VDD_EMM

C0_1P8_3P

3

VDD_ENET

0_VSELEC

T_1P8_2P5

_3P3

ENET0_RG

MII_RXD1

ESAI0_TX3

_RX2

SPI3_CS0 SPI3_SCK

E

DDR_DCF1

5

DDR_DCF0

3

DDR_DCF2

2

DDR_DCF3

2

DDR_DCF2

7

PCIE_CTR

L0_CLKRE

Q_B

EMMC0_C

MD

EMMC0_D

ATA6

VSS_MAIN

EMMC0_D

ATA3

VDD_ENET

0_1P8_2P5

_3P3

ESAI0_FST ESAI0_TX1

SPDIF0_EX

T_CLK

UART1_RX

F VSS_MAIN VSS_MAIN VSS_MAIN VSS_MAIN DDR_ZQ

PCIE_REF_

QR

EMMC0_C

LK

EMMC0_D

ATA5

EMMC0_D

ATA1

ENET0_RG

MII_TXD0

ENET0_RE

FCLK_125

M_25M

SPDIF0_RX

VDD_ENET

_MDIO_1P

8_3P3

SPI3_CS1

G

DDR_DCF1

0

DDR_CK0_

N

DDR_DCF0

0

DDR_DCF3

3

DDR_DCF3

1

PCIE0_PHY

_PLL_REF

_RETURN

USB_SS3_

TC1

EMMC0_D

ATA2

EMMC0_D

ATA4

ENET0_RG

MII_TXC

ENET0_RG

MII_RXD2

ESAI0_TX0 SPI3_SDO

UART1_CT

S_B

UART1_RT

S_B

H

DDR_CK0_

P

DDR_DCF2

4

DDR_DCF1

9

DDR_DCF3

0

DDR_DCF2

5

PCIE_REX

T

USB_SS3_

TC3

EMMC0_D

ATA7

ENET0_RG

MII_TX_CT

L

ENET0_RG

MII_RX_CT

L

ESAI0_SCK

R

SPI3_SDI VSS_MAIN SPI0_CS0

J VSS_MAIN VSS_MAIN VSS_MAIN VSS_MAIN

VDD_PCIE

_DIG_1P8_

3P3

VDD_PCIE

_1P8

VSS_MAIN

USB_OTG1

_VBUS

EMMC0_S

TROBE

ENET0_RG

MII_TXD2

ENET0_MD

IO

SPDIF0_TX UART1_TX SPI0_SDO SPI0_SDI

K

DDR_DCF0

8

DDR_DCF1

4

DDR_DCF0

4

VDD_DDR_

VDDQ

VDD_ANA0

_1P8

VDD_PCIE

_LDO_1P0

_CAP

VDD_USB_

1P8

VDD_MAIN VSS_MAIN VDD_GPU

ESAI0_TX5

_RX0

MCLK_OU

T0

VDD_ESAI

_SPDIF_1P

8_2P5_3P3

SPI0_CS1

L

DDR_DCF1

1

DDR_DCF0

9

DDR_DCF2

3

DDR_DCF1

6

VSS_MAIN VSS_MAIN VDD_MAIN VSS_MAIN VDD_GPU VDD_GPU VDD_MAIN MCLK_IN0 SPI0_SCK

VDD_SPI_

MCLK_UA

RT_1P8_3

P3

VSS_MAIN

M VSS_MAIN VSS_MAIN VSS_MAIN

VDD_DDR_

VDDQ

VDD_MAIN VSS_MAIN VDD_MAIN VSS_MAIN VDD_GPU VSS_MAIN MCLK_IN1 VSS_MAIN VSS_MAIN

ADC_VREF

H

N DDR_DQ02 DDR_DQ00 DDR_DQ13 DDR_DQ15

VDD_DDR_

VDDQ

VDD_MAIN VSS_MAIN VDD_MAIN VSS_MAIN VDD_GPU VSS_MAIN ADC_IN1 ADC_IN3 ADC_IN2

ADC_VREF

L

P DDR_DQ01 DDR_DQ12 DDR_DQ14

VDD_DDR_

VDDQ

VSS_MAIN VDD_MAIN VSS_MAIN VDD_MAIN VSS_MAIN VDD_GPU

VDD_ADC_

1P8

ADC_IN0 ADC_IN5 ADC_IN4

R VSS_MAIN VSS_MAIN VSS_MAIN VSS_MAIN VSS_MAIN VSS_MAIN VDD_MAIN VSS_MAIN VDD_GPU VSS_MAIN VDD_MAIN VSS_MAIN VSS_MAIN VSS_MAIN VSS_MAIN

T DDR_DQ03

DDR_DQS

1_N

DDR_DM1

VDD_DDR_

VDDQ

VDD_MAIN VSS_MAIN VDD_MAIN VSS_MAIN VDD_GPU VSS_MAIN

FLEXCAN0

_RX

FLEXCAN1

_RX

VDD_ADC_

DIG_1P8

FLEXCAN2

_RX

U

DDR_DQS

0_N

DDR_DQS

0_P

DDR_DQS

1_P

DDR_DTO0

VDD_DDR_

VDDQ

VDD_MAIN VSS_MAIN VDD_MAIN VSS_MAIN VDD_MAIN

VDD_CAN_

UART_1P8

_3P3

UART0_TX

FLEXCAN0

_TX

FLEXCAN2

_TX

FLEXCAN1

_TX

V VSS_MAIN VSS_MAIN VSS_MAIN

VDD_DDR_

VDDQ

VSS_MAIN VDD_A35 VDD_A35 VDD_A35 VSS_MAIN VDD_MAIN

MIPI_DSI0_

I2C0_SDA

VSS_MAIN UART2_TX UART0_RX

W DDR_DM0 DDR_DQ10 DDR_ATO

VDD_DDR_

PLL_1P8

VSS_MAIN VSS_MAIN VDD_A35 VDD_A35 VDD_A35 VSS_MAIN

VDD_ANA1

_1P8

JTAG_TMS

MIPI_DSI1_

I2C0_SDA

MIPI_DSI0_

I2C0_SCL

UART2_RX

Y DDR_DQ04 DDR_DQ08 DDR_VREF

VDD_DDR_

VDDQ

VDD_MAIN VSS_MAIN VDD_MAIN VSS_MAIN VDD_MAIN VSS_MAIN

SCU_GPIO

0_00

JTAG_TDO

VDD_SNVS

_4P2

MIPI_DSI1_

I2C0_SCL

AA VSS_MAIN VSS_MAIN VSS_MAIN VSS_MAIN

VDD_DDR_

VDDQ

VDD_MAIN

VDD_MIPI_

1P8

VDD_MIPI_

1P0

VSS_MAIN VDD_MAIN

VDD_TMP

R_CSI_1P8

_3P3

PMIC_INT_

B

TEST_MO

DE_SELEC

T

VSS_MAIN JTAG_TCK

AB DDR_DQ05 DDR_DQ11 DDR_DTO1

VDD_DDR_

VDDQ

QSPI0A_D

QS

QSPI0A_S

S0_B

VDD_MIPI_

1P8

VDD_MIPI_

1P0

VDD_MIPI_

CSI_DIG_1

P8

PMIC_ON_

REQ

SCU_BOO

T_MODE3

SCU_PMIC

_STANDBY

VDD_SNVS

_LDO_1P8

_CAP

JTAG_TRS

T_B

AC DDR_DQ06 DDR_DQ07 DDR_DQ09

QSPI0B_D

ATA0

QSPI0A_D

ATA2

MIPI_CSI0_

DATA3_N

MIPI_CSI0_

DATA1_N

MIPI_CSI0_

CLK_N

MIPI_CSI0_

DATA0_N

MIPI_CSI0_

DATA2_N

CSI_D00

SCU_BOO

T_MODE1

SCU_GPIO

0_01

PMIC_I2C_

SCL

JTAG_TDI

AD VSS_MAIN VSS_MAIN VSS_MAIN

VDD_QSPI

0A_1P8_3P

3

QSPI0A_S

S1_B

MIPI_CSI0_

DATA3_P

MIPI_CSI0_

DATA1_P

MIPI_CSI0_

CLK_P

MIPI_CSI0_

DATA0_P

MIPI_CSI0_

DATA2_P

CSI_D02 VSS_MAIN

SCU_BOO

T_MODE0

POR_B

AE

QSPI0B_D

ATA1

QSPI0B_D

ATA3

VDD_QSPI

0B_1P8_3P

3

QSPI0B_S

S0_B

VSS_MAIN VSS_MAIN VSS_MAIN VSS_MAIN VSS_MAIN VSS_MAIN VSS_MAIN

ANA_TEST

_OUT_P

SCU_BOO

T_MODE2

VSS_MAIN

PMIC_I2C_

SDA

AF

QSPI0B_D

ATA2

QSPI0B_D

QS

QSPI0B_S

S1_B

MIPI_DSI1_

DATA0_N

MIPI_DSI1_

DATA1_N

MIPI_DSI0_

DATA3_N

MIPI_DSI0_

CLK_N

MIPI_DSI0_

DATA2_N

MIPI_CSI0_

MCLK_OU

T

CSI_VSYN

C

VDD_CSI_1

P8_3P3

ANA_TEST

_OUT_N

RTC_XTAL

O

XTALO

AG VSS_MAIN

QSPI0A_S

CLK

QSPI0A_D

ATA3

MIPI_DSI1_

DATA2_N

MIPI_DSI1_

CLK_N

MIPI_DSI1_

DATA3_N

MIPI_DSI0_

DATA1_N

MIPI_DSI0_

DATA0_N

VSS_MAIN CSI_PCLK CSI_D04 CSI_D03 VSS_MAIN

VSS_SCU_

XTAL

VSS_SCU_

XTAL

AH

QSPI0B_S

CLK

QSPI0A_D

ATA1

VSS_MAIN

MIPI_DSI1_

DATA0_P

MIPI_DSI1_

DATA1_P

MIPI_DSI0_

DATA3_P

MIPI_DSI0_

CLK_P

MIPI_DSI0_

DATA2_P

CSI_RESE

T

CSI_HSYN

C

CSI_D07 CSI_D01 RTC_XTALI XTALI

AJ VSS_MAIN

QSPI0A_D

ATA0

MIPI_DSI1_

DATA2_P

MIPI_DSI1_

CLK_P

MIPI_DSI1_

DATA3_P

MIPI_DSI0_

DATA1_P

MIPI_DSI0_

DATA0_P

CSI_EN CSI_MCLK CSI_D06 CSI_D05

ON_OFF_B

UTTON

VSS_SCU_

XTAL

Package information and functional contact assignments for FCPBGA, 17 x 17 mm, 0.8 mm pitch

i.

MX 8QuadXPlus/8DualXPlus Automotive and Infotainment Applications Processors, Rev. 0, 11/2018

NXP Semiconductors

130

PRELIMINARY