User's Manual

Table Of Contents

APPLICANT: MOTOROLA EQUIPMENT TYPE: ABZ89FC5812

User / Operational Manual

Functional Description / Operation of Modules and Interconnect (Draft)

EXHIBIT D1-6

Control Module Overview

The transceiver control circuitry performs the digital signal processing data formatting for the base radio (BR) and

provides the external interfaces to the rest of the communication equipment present at the site. The Host

Processor is the MPC8250 and the DSP is the MSC8101. General functionality includes:

• Data and Control interface to the Receiver chip set devices

• Data and Control interface to the Exciter chip set devices

• Block Encoder / Decoder Interface

• DSP interfaces

• DSP / Host interface

• Host bus size and speed

• Host memory size, speed, and types supported

• External ports (ethernet, RS232, etc.)

• External physical interfaces (switches, connectors, etc.)

Control Switches

There is one switch on the Front Panel of the XCVR Control Module. The function of this multifunction switch can

be seen in the table below. The switch is debounced in hardware for 100 ms for the “less than 1 second” case.

When the switch is pressed for greater than 3 seconds a “PreReset” signal is sent to the Host processor via the

CPLDs IRQ1x signal followed by the actual reset command 1 second later.

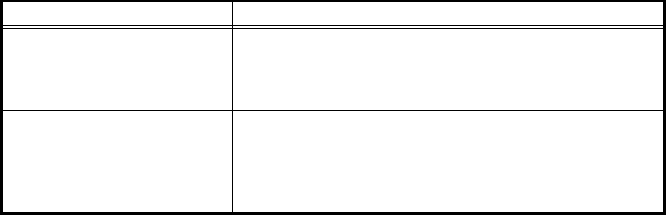

Switch Functions

Switch Function

Switch1

Pressed for less than 1

second

(See note)

(Application Specific)

When this switch closure conditions are met, the

Host CPLD/FPGA will generate an interrupt on

IRQ2x

Switch1 -

Pressed for greater than 3

seconds

XCVR Control Module Reset

When these switch closure conditions are met the

Host CPLD/FPGA will generate a Pre-reset signal

to the MPC8250 via IRQ1x of the CPLD followed by

a HRESET one second later.

Note: This switch function can be SW controlled. The typical usage for this switch is Access Disable, which

disables the power amplifier.