Datasheet

PIC18F2XK20/4XK20

DS41303G-page 46 2010 Microchip Technology Inc.

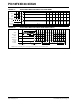

FIGURE 3-1: TRANSITION TIMING FOR ENTRY TO SLEEP MODE

FIGURE 3-2: TRANSITION TIMING FOR WAKE FROM SLEEP (HSPLL)

Q4Q3Q2

OSC1

Peripheral

Sleep

Program

Q1Q1

Counter

Clock

CPU

Clock

PC + 2PC

Q3 Q4 Q1 Q2

OSC1

Peripheral

Program

PC

PLL Clock

Q3 Q4

Output

CPU Clock

Q1 Q2 Q3 Q4 Q1 Q2

Clock

Counter

PC + 6

PC + 4

Q1 Q2 Q3 Q4

Wake Event

Note1: T

OST = 1024 TOSC; TPLL = 2 ms (approx). These intervals are not shown to scale.

TOST

(1)

TPLL

(1)

OSTS bit set

PC + 2